PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

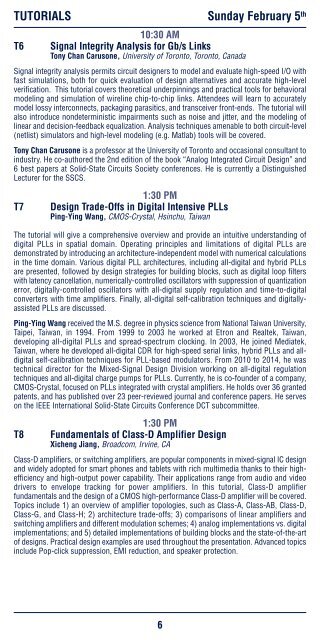

TUTORIALS<br />

10:30 AM<br />

T6 Signal Integrity Analysis for Gb/s Links<br />

Tony Chan Carusone, University of Toronto, Toronto, Canada<br />

Signal integrity analysis permits circuit designers to model and evaluate high-speed I/O with<br />

fast simulations, both for quick evaluation of design alternatives and accurate high-level<br />

verification. This tutorial covers theoretical underpinnings and practical tools for behavioral<br />

modeling and simulation of wireline chip-to-chip links. Attendees will learn to accurately<br />

model lossy interconnects, packaging parasitics, and transceiver front-ends. The tutorial will<br />

also introduce nondeterministic impairments such as noise and jitter, and the modeling of<br />

linear and decision-feedback equalization. Analysis techniques amenable to both circuit-level<br />

(netlist) simulators and high-level modeling (e.g. Matlab) tools will be covered.<br />

Tony Chan Carusone is a professor at the University of Toronto and occasional consultant to<br />

industry. He co-authored the 2nd edition of the book “Analog Integrated Circuit Design” and<br />

6 best papers at Solid-State Circuits Society conferences. He is currently a Distinguished<br />

Lecturer for the SSCS.<br />

T7<br />

1:30 PM<br />

Design Trade-Offs in Digital Intensive PLLs<br />

Ping-Ying Wang, CMOS-Crystal, Hsinchu, Taiwan<br />

Sunday February 5 th<br />

The tutorial will give a comprehensive overview and provide an intuitive understanding of<br />

digital PLLs in spatial domain. Operating principles and limitations of digital PLLs are<br />

demonstrated by introducing an architecture-independent model with numerical calculations<br />

in the time domain. Various digital PLL architectures, including all-digital and hybrid PLLs<br />

are presented, followed by design strategies for building blocks, such as digital loop filters<br />

with latency cancellation, numerically-controlled oscillators with suppression of quantization<br />

error, digitally-controlled oscillators with all-digital supply regulation and time-to-digital<br />

converters with time amplifiers. Finally, all-digital self-calibration techniques and digitallyassisted<br />

PLLs are discussed.<br />

Ping-Ying Wang received the M.S. degree in physics science from National Taiwan University,<br />

Taipei, Taiwan, in 1994. From 1999 to 2003 he worked at Etron and Realtek, Taiwan,<br />

developing all-digital PLLs and spread-spectrum clocking. In 2003, He joined Mediatek,<br />

Taiwan, where he developed all-digital CDR for high-speed serial links, hybrid PLLs and alldigital<br />

self-calibration techniques for PLL-based modulators. From 2010 to 2014, he was<br />

technical director for the Mixed-Signal Design Division working on all-digital regulation<br />

techniques and all-digital charge pumps for PLLs. Currently, he is co-founder of a company,<br />

CMOS-Crystal, focused on PLLs integrated with crystal amplifiers. He holds over 36 granted<br />

patents, and has published over 23 peer-reviewed journal and conference papers. He serves<br />

on the IEEE International Solid-State Circuits Conference DCT subcommittee.<br />

1:30 PM<br />

T8 Fundamentals of Class-D Amplifier Design<br />

Xicheng Jiang, Broadcom, Irvine, CA<br />

Class-D amplifiers, or switching amplifiers, are popular components in mixed-signal IC design<br />

and widely adopted for smart phones and tablets with rich multimedia thanks to their highefficiency<br />

and high-output power capability. Their applications range from audio and video<br />

drivers to envelope tracking for power amplifiers. In this tutorial, Class-D amplifier<br />

fundamentals and the design of a CMOS high-performance Class-D amplifier will be covered.<br />

Topics include 1) an overview of amplifier topologies, such as Class-A, Class-AB, Class-D,<br />

Class-G, and Class-H; 2) architecture trade-offs; 3) comparisons of linear amplifiers and<br />

switching amplifiers and different modulation schemes; 4) analog implementations vs. digital<br />

implementations; and 5) detailed implementations of building blocks and the state-of-the-art<br />

of designs. Practical design examples are used throughout the presentation. Advanced topics<br />

include Pop-click suppression, EMI reduction, and speaker protection.<br />

6