- Page 1 and 2:

VxWorks 5.5/Tornado 2.2 BSP Rel. 1

- Page 3:

222913 410 000 AA World Wide Web: w

- Page 6 and 7:

Serial Console . . . . . . . . . .

- Page 8 and 9:

External Interface . . . . . . . .

- Page 10 and 11:

Case B: When PPMC-275 is Non-Monarc

- Page 12 and 13:

xii VxWorks 5.5/Tornado 2.2 BSP Rel

- Page 14 and 15:

DRAM Dynamic Random Access Memory E

- Page 16 and 17:

Other Sources of Information For fu

- Page 19 and 20:

Introduction System Architecture Sy

- Page 21 and 22:

Introduction System Environment Sys

- Page 23 and 24:

Introduction Board Settings Table 2

- Page 25:

2 PPMC-275 BSP Features

- Page 28 and 29:

BSP Features PPMC-275 BSP Features

- Page 30 and 31:

BSP Features PPMC-275 BSP Features

- Page 32 and 33:

BSP Features PPMC-275 BSP Features

- Page 35 and 36:

Single CPU Configuration Single CPU

- Page 37:

4 Software Basics

- Page 40 and 41:

System Software Preparation Softwar

- Page 43 and 44:

API Call Reference List of APIs Lis

- Page 45 and 46:

API Call Reference List of APIs Tab

- Page 47 and 48:

API Call Reference List of APIs Sof

- Page 49 and 50:

API Call Reference List of APIs ISR

- Page 51 and 52:

API Call Reference List of APIs RET

- Page 53 and 54:

API Call Reference List of APIs Sys

- Page 55 and 56:

API Call Reference List of APIs Req

- Page 57 and 58:

API Call Reference List of APIs int

- Page 59 and 60:

API Call Reference List of APIs PCI

- Page 61 and 62:

API Call Reference List of APIs Var

- Page 63 and 64:

API Call Reference List of APIs use

- Page 65 and 66: API Call Reference List of APIs RET

- Page 67 and 68: API Call Reference List of APIs Ope

- Page 69 and 70: API Call Reference List of APIs INP

- Page 71 and 72: API Call Reference List of APIs INP

- Page 73 and 74: API Call Reference List of APIs int

- Page 75 and 76: API Call Reference List of APIs INP

- Page 77 and 78: API Call Reference List of APIs uns

- Page 79 and 80: API Call Reference List of APIs uns

- Page 81 and 82: API Call Reference List of APIs RET

- Page 83 and 84: API Call Reference List of APIs voi

- Page 85 and 86: API Call Reference List of APIs Com

- Page 87 and 88: API Call Reference List of APIs sdm

- Page 89 and 90: API Call Reference List of APIs Tab

- Page 91 and 92: API Call Reference List of APIs Tab

- Page 93 and 94: API Call Reference List of APIs Tab

- Page 95 and 96: API Call Reference List of APIs Tab

- Page 97 and 98: API Call Reference List of APIs Tab

- Page 99 and 100: API Call Reference List of APIs Ext

- Page 101 and 102: API Call Reference List of APIs boo

- Page 103 and 104: API Call Reference List of APIs PKT

- Page 105 and 106: API Call Reference List of APIs SDM

- Page 107 and 108: API Call Reference List of APIs STA

- Page 109 and 110: API Call Reference List of APIs INP

- Page 111 and 112: API Call Reference List of APIs Tab

- Page 113 and 114: API Call Reference List of APIs Tab

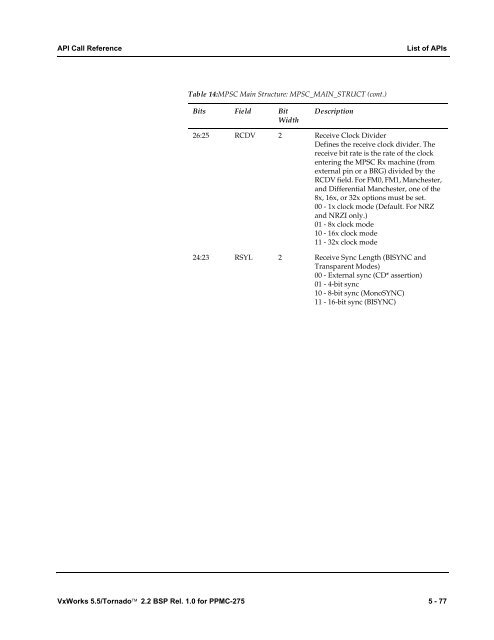

- Page 115: API Call Reference List of APIs Tab

- Page 119 and 120: API Call Reference List of APIs Tab

- Page 121 and 122: API Call Reference List of APIs Tab

- Page 123 and 124: API Call Reference List of APIs Tab

- Page 125 and 126: API Call Reference List of APIs Res

- Page 127 and 128: API Call Reference List of APIs INP

- Page 129 and 130: API Call Reference List of APIs Sof

- Page 131 and 132: API Call Reference List of APIs Th

- Page 133 and 134: API Call Reference List of APIs INP

- Page 135 and 136: API Call Reference List of APIs OUT

- Page 137 and 138: API Call Reference List of APIs RET

- Page 139 and 140: API Call Reference List of APIs INP

- Page 141 and 142: API Call Reference List of APIs INP

- Page 143 and 144: API Call Reference List of APIs voi

- Page 145 and 146: API Call Reference List of APIs RET

- Page 147 and 148: API Call Reference List of APIs Dev

- Page 149 and 150: API Call Reference List of APIs boo

- Page 151 and 152: API Call Reference List of APIs Sup

- Page 153 and 154: API Call Reference List of APIs OUT

- Page 155 and 156: API Call Reference List of APIs OUT

- Page 157 and 158: API Call Reference List of APIs Sof

- Page 159 and 160: API Call Reference List of APIs INP

- Page 161 and 162: API Call Reference List of APIs Boo

- Page 163 and 164: API Call Reference List of APIs RET

- Page 165 and 166: API Call Reference List of APIs Sup

- Page 167 and 168:

API Call Reference List of APIs Fla

- Page 169 and 170:

API Call Reference List of APIs RET

- Page 171 and 172:

API Call Reference List of APIs INP

- Page 173 and 174:

API Call Reference List of APIs OUT

- Page 175 and 176:

API Call Reference List of APIs Sof

- Page 177 and 178:

API Call Reference List of APIs INP

- Page 179 and 180:

API Call Reference List of APIs Ext

- Page 181 and 182:

API Call Reference List of APIs RET

- Page 183 and 184:

API Call Reference List of APIs siz

- Page 185 and 186:

API Call Reference List of APIs voi

- Page 187 and 188:

API Call Reference List of APIs OUT

- Page 189 and 190:

API Call Reference List of APIs int

- Page 191 and 192:

API Call Reference List of APIs voi

- Page 193 and 194:

API Call Reference List of APIs To

- Page 195 and 196:

API Call Reference List of APIs INP

- Page 197:

A Appendix

- Page 200 and 201:

Memory Map Memory Map The following

- Page 202 and 203:

PCI Boot Procedure on PPMC-275 4. F

- Page 204 and 205:

Using Test Tool Main Menu Number Op

- Page 206 and 207:

Using Test Tool Main Menu Number Op

- Page 208 and 209:

Using Test Tool Main Menu Number Op

- Page 210 and 211:

Using Test Tool Main Menu Number Op

- Page 213 and 214:

Reboot Feature Reboot Feature Reboo

- Page 215 and 216:

Index of Functions Functions bool e

- Page 217 and 218:

void gtUartBaudRateChange() 5-155 v

- Page 219:

Product Error Report Product: Seria