2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

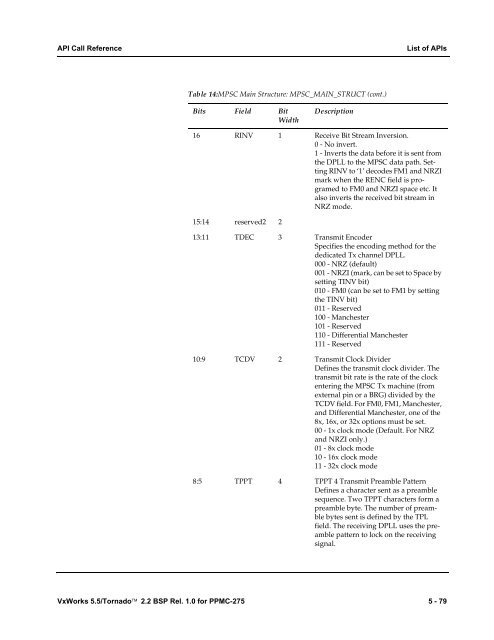

API Call Reference List of APIs<br />

Table 14:MPSC Main Structure: MPSC_MAIN_STRUCT (cont.)<br />

Bits Field Bit<br />

Width<br />

16 RINV 1 Receive Bit Stream Inversion.<br />

0 - No invert.<br />

1 - Inverts the data be<strong>for</strong>e it is sent from<br />

the DPLL to the MPSC data path. Setting<br />

RINV to ‘1’ decodes FM1 and NRZI<br />

mark when the RENC field is programed<br />

to FM0 and NRZI space etc. It<br />

also inverts the received bit stream in<br />

NRZ mode.<br />

15:14 reserved2 2<br />

Description<br />

13:11 TDEC 3 Transmit Encoder<br />

Specifies the encoding method <strong>for</strong> the<br />

dedicated Tx channel DPLL.<br />

000 - NRZ (default)<br />

001 - NRZI (mark, can be set to Space by<br />

setting TINV bit)<br />

010 - FM0 (can be set to FM1 by setting<br />

the TINV bit)<br />

011 - Reserved<br />

100 - Manchester<br />

101 - Reserved<br />

110 - Differential Manchester<br />

111 - Reserved<br />

10:9 TCDV 2 Transmit Clock Divider<br />

Defines the transmit clock divider. The<br />

transmit bit rate is the rate of the clock<br />

entering the MPSC Tx machine (from<br />

external pin or a BRG) divided by the<br />

TCDV field. For FM0, FM1, Manchester,<br />

and Differential Manchester, one of the<br />

8x, 16x, or 32x options must be set.<br />

00 - 1x clock mode (Default. For NRZ<br />

and NRZI only.)<br />

01 - 8x clock mode<br />

10 - 16x clock mode<br />

11 - 32x clock mode<br />

8:5 TPPT 4 TPPT 4 Transmit Preamble Pattern<br />

Defines a character sent as a preamble<br />

sequence. Two TPPT characters <strong>for</strong>m a<br />

preamble byte. The number of preamble<br />

bytes sent is defined by the TPL<br />

field. The receiving DPLL uses the preamble<br />

pattern to lock on the receiving<br />

signal.<br />

VxWorks 5.5/Tornado <strong>2.2</strong> <strong>BSP</strong> <strong>Rel</strong>. <strong>1.0</strong> <strong>for</strong> <strong>PPMC</strong>-<strong>275</strong> 5 - 79