2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

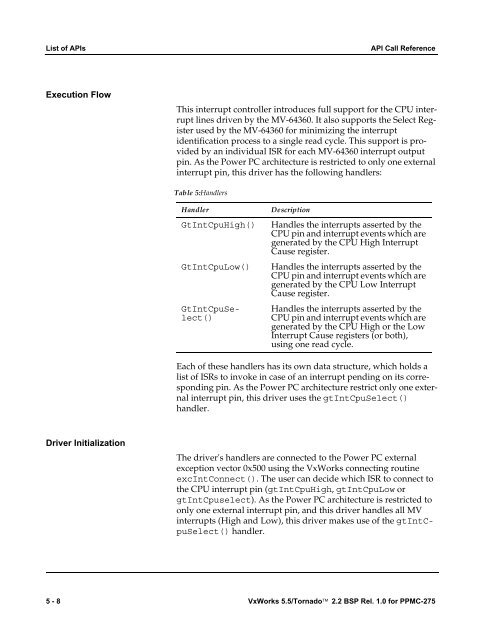

List of APIs API Call Reference<br />

Execution Flow<br />

Driver Initialization<br />

This interrupt controller introduces full support <strong>for</strong> the CPU interrupt<br />

lines driven by the MV-64360. It also supports the Select Register<br />

used by the MV-64360 <strong>for</strong> minimizing the interrupt<br />

identification process to a single read cycle. This support is provided<br />

by an individual ISR <strong>for</strong> each MV-64360 interrupt output<br />

pin. As the Power PC architecture is restricted to only one external<br />

interrupt pin, this driver has the following handlers:<br />

Table 5:Handlers<br />

Handler Description<br />

GtIntCpuHigh() Handles the interrupts asserted by the<br />

CPU pin and interrupt events which are<br />

generated by the CPU High Interrupt<br />

Cause register.<br />

GtIntCpuLow() Handles the interrupts asserted by the<br />

CPU pin and interrupt events which are<br />

generated by the CPU Low Interrupt<br />

Cause register.<br />

GtIntCpuSelect()<br />

Handles the interrupts asserted by the<br />

CPU pin and interrupt events which are<br />

generated by the CPU High or the Low<br />

Interrupt Cause registers (or both),<br />

using one read cycle.<br />

Each of these handlers has its own data structure, which holds a<br />

list of ISRs to invoke in case of an interrupt pending on its corresponding<br />

pin. As the Power PC architecture restrict only one external<br />

interrupt pin, this driver uses the gtIntCpuSelect()<br />

handler.<br />

The driver's handlers are connected to the Power PC external<br />

exception vector 0x500 using the VxWorks connecting routine<br />

excIntConnect(). The user can decide which ISR to connect to<br />

the CPU interrupt pin (gtIntCpuHigh, gtIntCpuLow or<br />

gtIntCpuselect). As the Power PC architecture is restricted to<br />

only one external interrupt pin, and this driver handles all MV<br />

interrupts (High and Low), this driver makes use of the gtIntCpuSelect()<br />

handler.<br />

5 - 8 VxWorks 5.5/Tornado <strong>2.2</strong> <strong>BSP</strong> <strong>Rel</strong>. <strong>1.0</strong> <strong>for</strong> <strong>PPMC</strong>-<strong>275</strong>