2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

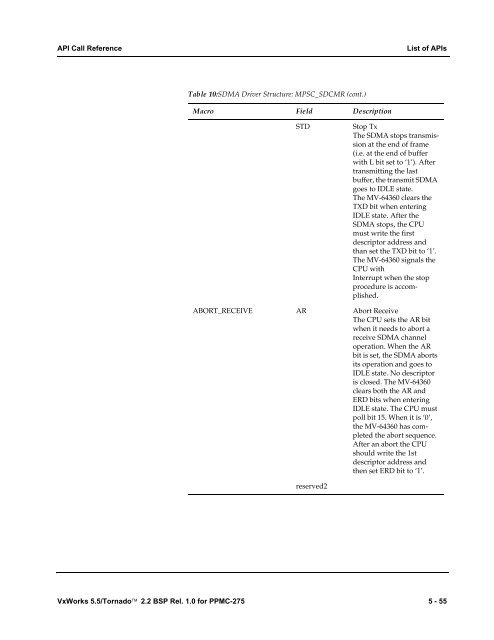

API Call Reference List of APIs<br />

Table 10:SDMA Driver Structure: MPSC_SDCMR (cont.)<br />

Macro Field Description<br />

STD Stop Tx<br />

The SDMA stops transmission<br />

at the end of frame<br />

(i.e. at the end of buffer<br />

with L bit set to ‘1’). After<br />

transmitting the last<br />

buffer, the transmit SDMA<br />

goes to IDLE state.<br />

The MV-64360 clears the<br />

TXD bit when entering<br />

IDLE state. After the<br />

SDMA stops, the CPU<br />

must write the first<br />

descriptor address and<br />

than set the TXD bit to ‘1’.<br />

The MV-64360 signals the<br />

CPU with<br />

Interrupt when the stop<br />

procedure is accomplished.<br />

ABORT_RECEIVE AR Abort Receive<br />

The CPU sets the AR bit<br />

when it needs to abort a<br />

receive SDMA channel<br />

operation. When the AR<br />

bit is set, the SDMA aborts<br />

its operation and goes to<br />

IDLE state. No descriptor<br />

is closed. The MV-64360<br />

clears both the AR and<br />

ERD bits when entering<br />

IDLE state. The CPU must<br />

poll bit 15. When it is ‘0’,<br />

the MV-64360 has completed<br />

the abort sequence.<br />

After an abort the CPU<br />

should write the 1st<br />

descriptor address and<br />

then set ERD bit to ‘1’.<br />

reserved2<br />

VxWorks 5.5/Tornado <strong>2.2</strong> <strong>BSP</strong> <strong>Rel</strong>. <strong>1.0</strong> <strong>for</strong> <strong>PPMC</strong>-<strong>275</strong> 5 - 55