2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

2.2 BSP Rel. 1.0 for PPMC-275 Programmer's Guide

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

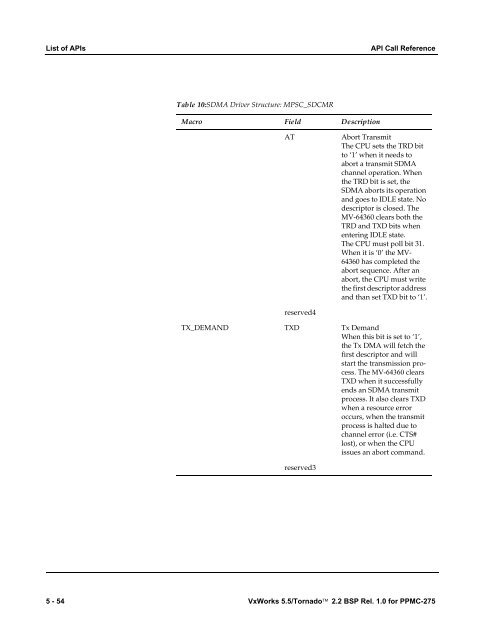

List of APIs API Call Reference<br />

Table 10:SDMA Driver Structure: MPSC_SDCMR<br />

Macro Field Description<br />

AT Abort Transmit<br />

The CPU sets the TRD bit<br />

to ‘1’ when it needs to<br />

abort a transmit SDMA<br />

channel operation. When<br />

the TRD bit is set, the<br />

SDMA aborts its operation<br />

and goes to IDLE state. No<br />

descriptor is closed. The<br />

MV-64360 clears both the<br />

TRD and TXD bits when<br />

entering IDLE state.<br />

The CPU must poll bit 31.<br />

When it is ‘0’ the MV-<br />

64360 has completed the<br />

abort sequence. After an<br />

abort, the CPU must write<br />

the first descriptor address<br />

and than set TXD bit to ‘1’.<br />

reserved4<br />

TX_DEMAND TXD Tx Demand<br />

When this bit is set to ‘1’,<br />

the Tx DMA will fetch the<br />

first descriptor and will<br />

start the transmission process.<br />

The MV-64360 clears<br />

TXD when it successfully<br />

ends an SDMA transmit<br />

process. It also clears TXD<br />

when a resource error<br />

occurs, when the transmit<br />

process is halted due to<br />

channel error (i.e. CTS#<br />

lost), or when the CPU<br />

issues an abort command.<br />

reserved3<br />

5 - 54 VxWorks 5.5/Tornado <strong>2.2</strong> <strong>BSP</strong> <strong>Rel</strong>. <strong>1.0</strong> <strong>for</strong> <strong>PPMC</strong>-<strong>275</strong>