channel - Advances in Electronics and Telecommunications

channel - Advances in Electronics and Telecommunications

channel - Advances in Electronics and Telecommunications

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

MOY AND RAULET: HIGH-LEVEL DESIGN METHODOLOGY FOR ULTRA-FAST SOFTWARE DEFINED RADIO PROTOTYPING 79<br />

Time<br />

FPGA1 Com/Transfer DSP Com/Transfer FPGA2<br />

Send_DSP_FPGA1<br />

IP_4 IP_3<br />

Send_FPGA1_DSP<br />

IP_1<br />

IP_2<br />

IP_5<br />

IP_6<br />

Send_DSP_FPGA2<br />

Send_FPGA2_DSP<br />

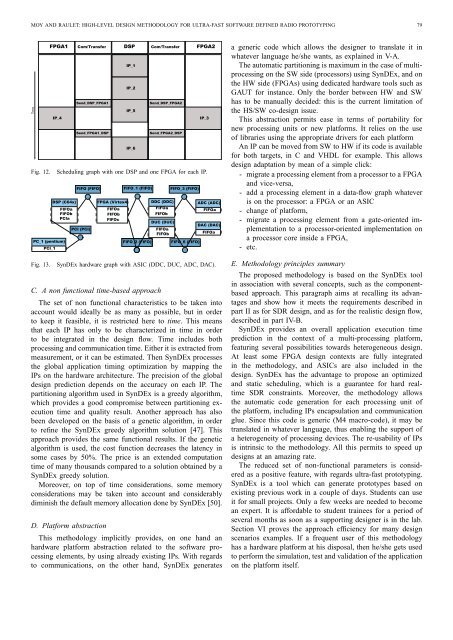

Fig. 12. Schedul<strong>in</strong>g graph with one DSP <strong>and</strong> one FPGA for each IP.<br />

PC_1 (pentium)<br />

PCI_1<br />

DSP (C64x)<br />

FIFOa<br />

FIFOb<br />

PCIa<br />

FIFO (FIFO)<br />

PCI (PCI)<br />

FPGA (Virtex4)<br />

FIFOa<br />

FIFOb<br />

FIFOc<br />

FIFO_1 (FIFO)<br />

FIFO_2 FIFO_5 FIFO_4 (FIFO (FIFO) )<br />

DDC (DDC)<br />

FIFOa<br />

FIFOb<br />

DUC (DUC)<br />

FIFOa<br />

FIFOb<br />

FIFO_3 (FIFO)<br />

FIFO_6 (FIFO)<br />

ADC (ADC)<br />

FIFOa<br />

DAC (DAC)<br />

FIFOa<br />

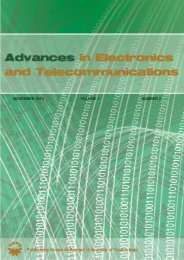

Fig. 13. SynDEx hardware graph with ASIC (DDC, DUC, ADC, DAC).<br />

C. A non functional time-based approach<br />

The set of non functional characteristics to be taken <strong>in</strong>to<br />

account would ideally be as many as possible, but <strong>in</strong> order<br />

to keep it feasible, it is restricted here to time. This means<br />

that each IP has only to be characterized <strong>in</strong> time <strong>in</strong> order<br />

to be <strong>in</strong>tegrated <strong>in</strong> the design flow. Time <strong>in</strong>cludes both<br />

process<strong>in</strong>g <strong>and</strong> communication time. Either it is extracted from<br />

measurement, or it can be estimated. Then SynDEx processes<br />

the global application tim<strong>in</strong>g optimization by mapp<strong>in</strong>g the<br />

IPs on the hardware architecture. The precision of the global<br />

design prediction depends on the accuracy on each IP. The<br />

partition<strong>in</strong>g algorithm used <strong>in</strong> SynDEx is a greedy algorithm,<br />

which provides a good compromise between partition<strong>in</strong>g execution<br />

time <strong>and</strong> quality result. Another approach has also<br />

been developed on the basis of a genetic algorithm, <strong>in</strong> order<br />

to ref<strong>in</strong>e the SynDEx greedy algorithm solution [47]. This<br />

approach provides the same functional results. If the genetic<br />

algorithm is used, the cost function decreases the latency <strong>in</strong><br />

some cases by 50%. The price is an extended computation<br />

time of many thous<strong>and</strong>s compared to a solution obta<strong>in</strong>ed by a<br />

SynDEx greedy solution.<br />

Moreover, on top of time considerations, some memory<br />

considerations may be taken <strong>in</strong>to account <strong>and</strong> considerably<br />

dim<strong>in</strong>ish the default memory allocation done by SynDEx [50].<br />

D. Platform abstraction<br />

This methodology implicitly provides, on one h<strong>and</strong> an<br />

hardware platform abstraction related to the software process<strong>in</strong>g<br />

elements, by us<strong>in</strong>g already exist<strong>in</strong>g IPs. With regards<br />

to communications, on the other h<strong>and</strong>, SynDEx generates<br />

a generic code which allows the designer to translate it <strong>in</strong><br />

whatever language he/she wants, as expla<strong>in</strong>ed <strong>in</strong> V-A.<br />

The automatic partition<strong>in</strong>g is maximum <strong>in</strong> the case of multiprocess<strong>in</strong>g<br />

on the SW side (processors) us<strong>in</strong>g SynDEx, <strong>and</strong> on<br />

the HW side (FPGAs) us<strong>in</strong>g dedicated hardware tools such as<br />

GAUT for <strong>in</strong>stance. Only the border between HW <strong>and</strong> SW<br />

has to be manually decided: this is the current limitation of<br />

the HS/SW co-design issue.<br />

This abstraction permits ease <strong>in</strong> terms of portability for<br />

new process<strong>in</strong>g units or new platforms. It relies on the use<br />

of libraries us<strong>in</strong>g the appropriate drivers for each platform<br />

An IP can be moved from SW to HW if its code is available<br />

for both targets, <strong>in</strong> C <strong>and</strong> VHDL for example. This allows<br />

design adaptation by mean of a simple click:<br />

- migrate a process<strong>in</strong>g element from a processor to a FPGA<br />

<strong>and</strong> vice-versa,<br />

- add a process<strong>in</strong>g element <strong>in</strong> a data-flow graph whatever<br />

is on the processor: a FPGA or an ASIC<br />

- change of platform,<br />

- migrate a process<strong>in</strong>g element from a gate-oriented implementation<br />

to a processor-oriented implementation on<br />

a processor core <strong>in</strong>side a FPGA,<br />

- etc.<br />

E. Methodology pr<strong>in</strong>ciples summary<br />

The proposed methodology is based on the SynDEx tool<br />

<strong>in</strong> association with several concepts, such as the componentbased<br />

approach. This paragraph aims at recall<strong>in</strong>g its advantages<br />

<strong>and</strong> show how it meets the requirements described <strong>in</strong><br />

part II as for SDR design, <strong>and</strong> as for the realistic design flow,<br />

described <strong>in</strong> part IV-B.<br />

SynDEx provides an overall application execution time<br />

prediction <strong>in</strong> the context of a multi-process<strong>in</strong>g platform,<br />

featur<strong>in</strong>g several possibilities towards heterogeneous design.<br />

At least some FPGA design contexts are fully <strong>in</strong>tegrated<br />

<strong>in</strong> the methodology, <strong>and</strong> ASICs are also <strong>in</strong>cluded <strong>in</strong> the<br />

design. SynDEx has the advantage to propose an optimized<br />

<strong>and</strong> static schedul<strong>in</strong>g, which is a guarantee for hard realtime<br />

SDR constra<strong>in</strong>ts. Moreover, the methodology allows<br />

the automatic code generation for each process<strong>in</strong>g unit of<br />

the platform, <strong>in</strong>clud<strong>in</strong>g IPs encapsulation <strong>and</strong> communication<br />

glue. S<strong>in</strong>ce this code is generic (M4 macro-code), it may be<br />

translated <strong>in</strong> whatever language, thus enabl<strong>in</strong>g the support of<br />

a heterogeneity of process<strong>in</strong>g devices. The re-usability of IPs<br />

is <strong>in</strong>tr<strong>in</strong>sic to the methodology. All this permits to speed up<br />

designs at an amaz<strong>in</strong>g rate.<br />

The reduced set of non-functional parameters is considered<br />

as a positive feature, with regards ultra-fast prototyp<strong>in</strong>g.<br />

SynDEx is a tool which can generate prototypes based on<br />

exist<strong>in</strong>g previous work <strong>in</strong> a couple of days. Students can use<br />

it for small projects. Only a few weeks are needed to become<br />

an expert. It is affordable to student tra<strong>in</strong>ees for a period of<br />

several months as soon as a support<strong>in</strong>g designer is <strong>in</strong> the lab.<br />

Section VI proves the approach efficiency for many design<br />

scenarios examples. If a frequent user of this methodology<br />

has a hardware platform at his disposal, then he/she gets used<br />

to perform the simulation, test <strong>and</strong> validation of the application<br />

on the platform itself.