Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

ADC 6640 ADC 6640<br />

DV<br />

AD6640<br />

AD6620<br />

BLOQUE DE ADQUISICIÓN<br />

32 MHZ<br />

Enable1<br />

BLOQUE DE ADQUISICIÓN<br />

MUX<br />

MUX<br />

DV<br />

JTAG<br />

FPGA<br />

FLEX 10K10<br />

FPGA<br />

FLEX 10K10<br />

BLOQUE DE CONTROL<br />

FIFO<br />

FIFO<br />

FIFO FIFO<br />

FIFO<br />

FIFO<br />

To PC<br />

ADC 6640 ADC 6640<br />

AD6640<br />

AD6620<br />

Channel<br />

BLOQUE DE CONTROL<br />

Channel<br />

Enable1<br />

Enable2<br />

32 MHZ<br />

FIFO<br />

BLOQUE DE ADQUISICIÓN<br />

Enable2<br />

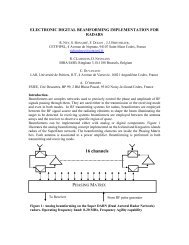

Figura 15 Diagrama <strong>de</strong> bloques <strong>de</strong>l equipo.<br />

Una vez que se encuentran habilitados los Receptores Digitales (al inicio <strong>de</strong> la adquisición) enviarán datos<br />

en forma continua y para po<strong>de</strong>r sincronizarlos, las señales <strong>de</strong>l Controlador <strong>de</strong> Radar ingresan en la Lógica <strong>de</strong><br />

Control y habilitan el paso <strong>de</strong> los datos hacia la FIFO y <strong>de</strong>spués a la PC.<br />

2.2.1 Bloque <strong>de</strong> Adquisición.<br />

Este bloque consta <strong>de</strong> dos partes principales, el ADC AD6640 y el Receptor Digital AD6620, cada cual<br />

con sus buffers e interfaces <strong>de</strong> entrada y salida para la adaptación <strong>de</strong> las señales tanto analógicas como digitales.<br />

2.2.1.1 Bloque <strong>de</strong> adquisición utilizando tarjetas <strong>de</strong> evaluación AD6620 y AD6640<br />

Estas tarjetas <strong>de</strong> evaluación son diseñadas por Analog Devices. La tarjeta <strong>de</strong> evaluación <strong>de</strong>l AD6620<br />

permite múltiples configuraciones las cuales se pue<strong>de</strong>n realizar por hardware (por medio <strong>de</strong> jumpers) o por<br />

software.<br />

En la figura 16 se observa el diagrama <strong>de</strong> bloques <strong>de</strong> estas tarjetas <strong>de</strong> evaluación. La tarjeta <strong>de</strong> evaluación<br />

<strong>de</strong>l AD6620, cuenta a<strong>de</strong>más con una memoria FIFO, que se utiliza para hacer lecturas <strong>de</strong> datos <strong>de</strong>l AD6620 o <strong>de</strong>l<br />

AD6640 y enviarlas por el puerto paralelo a una PC; por este mismo puerto se realiza la configuración <strong>de</strong>l AD6620.<br />

13