Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

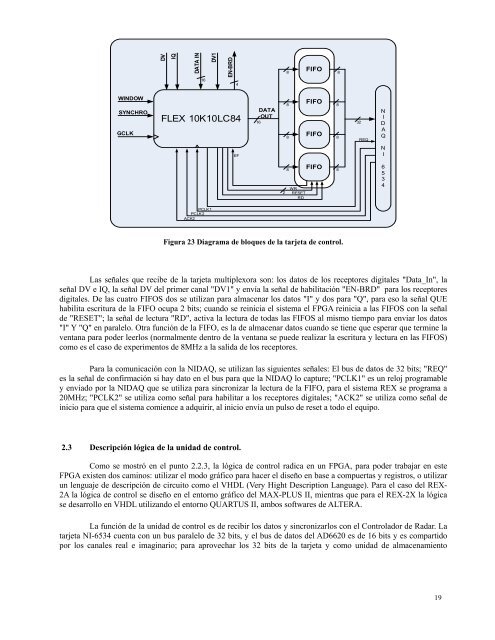

DV<br />

IQ<br />

DATA IN<br />

16<br />

DV1<br />

EN-BRD<br />

4<br />

FIFO<br />

8 8<br />

WINDOW<br />

SYNCHRO<br />

GCLK<br />

FLEX 10K10LC84<br />

DATA<br />

OUT<br />

16<br />

8<br />

8<br />

FIFO<br />

FIFO<br />

8<br />

8<br />

32<br />

REQ<br />

N<br />

I<br />

D<br />

A<br />

Q<br />

EF<br />

N<br />

I<br />

2<br />

8<br />

WR<br />

RESET<br />

RD<br />

FIFO<br />

8<br />

6<br />

5<br />

3<br />

4<br />

PCLK1<br />

PCLK2<br />

ACK2<br />

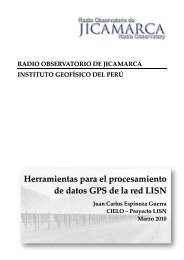

Figura 23 Diagrama <strong>de</strong> bloques <strong>de</strong> la tarjeta <strong>de</strong> control.<br />

Las señales que recibe <strong>de</strong> la tarjeta multiplexora son: los datos <strong>de</strong> los receptores digitales "Data_In", la<br />

señal DV e IQ, la señal DV <strong>de</strong>l primer canal "DV1" y envía la señal <strong>de</strong> habilitación "EN-BRD" para los receptores<br />

digitales. De las cuatro FIFOS dos se utilizan para almacenar los datos "I" y dos para "Q", para eso la señal QUE<br />

habilita escritura <strong>de</strong> la FIFO ocupa 2 bits; cuando se reinicia el sistema el FPGA reinicia a las FIFOS con la señal<br />

<strong>de</strong> "RESET"; la señal <strong>de</strong> lectura "RD", activa la lectura <strong>de</strong> todas las FIFOS al mismo tiempo para enviar los datos<br />

"I" Y "Q" en paralelo. Otra función <strong>de</strong> la FIFO, es la <strong>de</strong> almacenar datos cuando se tiene que esperar que termine la<br />

ventana para po<strong>de</strong>r leerlos (normalmente <strong>de</strong>ntro <strong>de</strong> la ventana se pue<strong>de</strong> realizar la escritura y lectura en las FIFOS)<br />

como es el caso <strong>de</strong> experimentos <strong>de</strong> 8MHz a la salida <strong>de</strong> los receptores.<br />

Para la comunicación con la NIDAQ, se utilizan las siguientes señales: El bus <strong>de</strong> datos <strong>de</strong> 32 bits; "REQ"<br />

es la señal <strong>de</strong> confirmación si hay dato en el bus para que la NIDAQ lo capture; "PCLK1" es un reloj programable<br />

y enviado por la NIDAQ que se utiliza para sincronizar la lectura <strong>de</strong> la FIFO, para el sistema <strong>REX</strong> se programa a<br />

20MHz; "PCLK2" se utiliza como señal para habilitar a los receptores digitales; "ACK2" se utiliza como señal <strong>de</strong><br />

inicio para que el sistema comience a adquirir, al inicio envía un pulso <strong>de</strong> reset a todo el equipo.<br />

2.3 Descripción lógica <strong>de</strong> la unidad <strong>de</strong> control.<br />

Como se mostró en el punto 2.2.3, la lógica <strong>de</strong> control radica en un FPGA, para po<strong>de</strong>r trabajar en este<br />

FPGA existen dos caminos: utilizar el modo gráfico para hacer el diseño en base a compuertas y registros, o utilizar<br />

un lenguaje <strong>de</strong> <strong>de</strong>scripción <strong>de</strong> circuito como el VHDL (Very Hight Description Language). Para el caso <strong>de</strong>l <strong>REX</strong>-<br />

2A la lógica <strong>de</strong> control se diseño en el entorno gráfico <strong>de</strong>l MAX-PLUS II, mientras que para el <strong>REX</strong>-<strong>2X</strong> la lógica<br />

se <strong>de</strong>sarrollo en VHDL utilizando el entorno QUARTUS II, ambos softwares <strong>de</strong> ALTERA.<br />

La función <strong>de</strong> la unidad <strong>de</strong> control es <strong>de</strong> recibir los datos y sincronizarlos con el Controlador <strong>de</strong> Radar. La<br />

tarjeta NI-6534 cuenta con un bus paralelo <strong>de</strong> 32 bits, y el bus <strong>de</strong> datos <strong>de</strong>l AD6620 es <strong>de</strong> 16 bits y es compartido<br />

por los canales real e imaginario; para aprovechar los 32 bits <strong>de</strong> la tarjeta y como unidad <strong>de</strong> almacenamiento<br />

19