Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

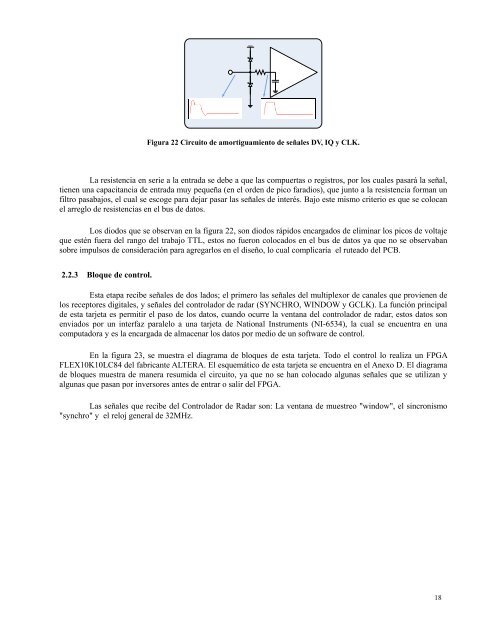

VCC<br />

Figura 22 Circuito <strong>de</strong> amortiguamiento <strong>de</strong> señales DV, IQ y CLK.<br />

La resistencia en serie a la entrada se <strong>de</strong>be a que las compuertas o registros, por los cuales pasará la señal,<br />

tienen una capacitancia <strong>de</strong> entrada muy pequeña (en el or<strong>de</strong>n <strong>de</strong> pico faradios), que junto a la resistencia forman un<br />

filtro pasabajos, el cual se escoge para <strong>de</strong>jar pasar las señales <strong>de</strong> interés. Bajo este mismo criterio es que se colocan<br />

el arreglo <strong>de</strong> resistencias en el bus <strong>de</strong> datos.<br />

Los diodos que se observan en la figura 22, son diodos rápidos encargados <strong>de</strong> eliminar los picos <strong>de</strong> voltaje<br />

que estén fuera <strong>de</strong>l rango <strong>de</strong>l trabajo TTL, estos no fueron colocados en el bus <strong>de</strong> datos ya que no se observaban<br />

sobre impulsos <strong>de</strong> consi<strong>de</strong>ración para agregarlos en el diseño, lo cual complicaría el ruteado <strong>de</strong>l PCB.<br />

2.2.3 Bloque <strong>de</strong> control.<br />

Esta etapa recibe señales <strong>de</strong> dos lados; el primero las señales <strong>de</strong>l multiplexor <strong>de</strong> canales que provienen <strong>de</strong><br />

los receptores digitales, y señales <strong>de</strong>l controlador <strong>de</strong> radar (SYNCHRO, WINDOW y GCLK). La función principal<br />

<strong>de</strong> esta tarjeta es permitir el paso <strong>de</strong> los datos, cuando ocurre la ventana <strong>de</strong>l controlador <strong>de</strong> radar, estos datos son<br />

enviados por un interfaz paralelo a una tarjeta <strong>de</strong> National Instruments (NI-6534), la cual se encuentra en una<br />

computadora y es la encargada <strong>de</strong> almacenar los datos por medio <strong>de</strong> un software <strong>de</strong> control.<br />

En la figura 23, se muestra el diagrama <strong>de</strong> bloques <strong>de</strong> esta tarjeta. Todo el control lo realiza un FPGA<br />

FLEX10K10LC84 <strong>de</strong>l fabricante ALTERA. El esquemático <strong>de</strong> esta tarjeta se encuentra en el Anexo D. El diagrama<br />

<strong>de</strong> bloques muestra <strong>de</strong> manera resumida el circuito, ya que no se han colocado algunas señales que se utilizan y<br />

algunas que pasan por inversores antes <strong>de</strong> entrar o salir <strong>de</strong>l FPGA.<br />

Las señales que recibe <strong>de</strong>l Controlador <strong>de</strong> Radar son: La ventana <strong>de</strong> muestreo "window", el sincronismo<br />

"synchro" y el reloj general <strong>de</strong> 32MHz.<br />

18