Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

(<strong>de</strong> los receptores digitales) y <strong>de</strong>l Controlador <strong>de</strong> Radar, basándose en la sincronización mostrada en el punto 2.3.2.<br />

• Bloque ADQ_NIDAQ: Encargada <strong>de</strong> controlar a los <strong>de</strong>más bloques <strong>de</strong>s<strong>de</strong> su habilitación, reseteo,<br />

escritura, lectura, escritura <strong>de</strong> marcas, etc.<br />

• Bloque PREPARE_SIGNAL: Se encarga <strong>de</strong> preparar las señales <strong>de</strong> escritura <strong>de</strong> datos para cada grupo <strong>de</strong><br />

FIFOS (I y Q) teniendo en cuenta que la escritura en la FIFO es asíncrona. A<strong>de</strong>más escribe las marcas.<br />

• Bloque FIFO_CONTROL: Es el encargado <strong>de</strong> la lectura y escritura <strong>de</strong> las FIFOS, para lo cual trabaja con<br />

dos relojes: El reloj general <strong>de</strong> 32MHz y el reloj <strong>de</strong> la NIDAQ <strong>de</strong> 20MHz.<br />

estado.<br />

A continuación se muestra <strong>de</strong>talladamente cada uno <strong>de</strong> estos bloques junto con sus tablas y máquinas <strong>de</strong><br />

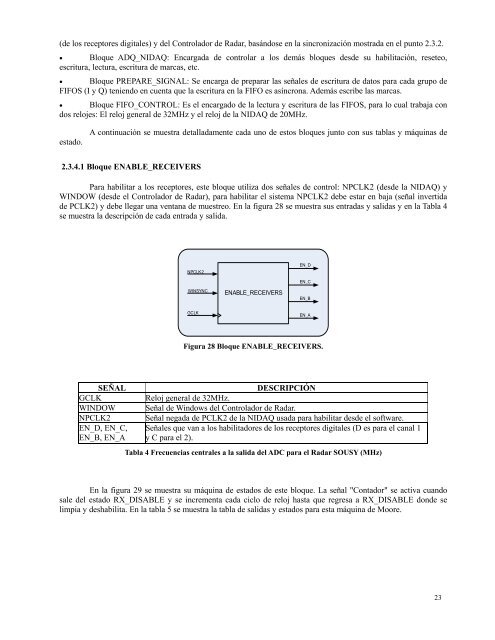

2.3.4.1 Bloque ENABLE_RECEIVERS<br />

Para habilitar a los receptores, este bloque utiliza dos señales <strong>de</strong> control: NPCLK2 (<strong>de</strong>s<strong>de</strong> la NIDAQ) y<br />

WINDOW (<strong>de</strong>s<strong>de</strong> el Controlador <strong>de</strong> Radar), para habilitar el sistema NPCLK2 <strong>de</strong>be estar en baja (señal invertida<br />

<strong>de</strong> PCLK2) y <strong>de</strong>be llegar una ventana <strong>de</strong> muestreo. En la figura 28 se muestra sus entradas y salidas y en la Tabla 4<br />

se muestra la <strong>de</strong>scripción <strong>de</strong> cada entrada y salida.<br />

NPCLK2<br />

EN_D<br />

WINSYNC<br />

ENABLE_RECEIVERS<br />

EN_C<br />

EN_B<br />

GCLK<br />

EN_A<br />

Figura 28 Bloque ENABLE_RECEIVERS.<br />

SEÑAL<br />

GCLK<br />

WINDOW<br />

NPCLK2<br />

EN_D, EN_C,<br />

EN_B, EN_A<br />

DESCRIPCIÓN<br />

Reloj general <strong>de</strong> 32MHz.<br />

Señal <strong>de</strong> Windows <strong>de</strong>l Controlador <strong>de</strong> Radar.<br />

Señal negada <strong>de</strong> PCLK2 <strong>de</strong> la NIDAQ usada para habilitar <strong>de</strong>s<strong>de</strong> el software.<br />

Señales que van a los habilitadores <strong>de</strong> los receptores digitales (D es para el canal 1<br />

y C para el 2).<br />

Tabla 4 Frecuencias centrales a la salida <strong>de</strong>l ADC para el Radar SOUSY (MHz)<br />

En la figura 29 se muestra su máquina <strong>de</strong> estados <strong>de</strong> este bloque. La señal "Contador" se activa cuando<br />

sale <strong>de</strong>l estado RX_DISABLE y se incrementa cada ciclo <strong>de</strong> reloj hasta que regresa a RX_DISABLE don<strong>de</strong> se<br />

limpia y <strong>de</strong>shabilita. En la tabla 5 se muestra la tabla <strong>de</strong> salidas y estados para esta máquina <strong>de</strong> Moore.<br />

23