Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Proyecto REX-2X - Radio Observatorio de Jicamarca

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SISTEMA DE ADQUISICIÓN UTILIZANDO RECEPTORES DIGITALES<br />

PROYECTO <strong>REX</strong>-<strong>2X</strong><br />

1. INTRODUCCIÓN<br />

El sistema <strong>REX</strong> es un equipo que utiliza como núcleo principal receptores digitales AD6620, los cuales<br />

son circuitos integrados DSP para aplicaciones comerciales. Con estos receptores se pue<strong>de</strong> realizar operaciones<br />

digitales que anteriormente se hacían <strong>de</strong> forma analógica, así como <strong>de</strong>modulación en cuadratura, filtrado y<br />

<strong>de</strong>cimación.<br />

<strong>REX</strong> es el pre<strong>de</strong>cesor <strong>de</strong> un proyecto <strong>de</strong>nominado Sistema NATALIA, en el cual la <strong>de</strong>modulación y<br />

filtrado se realizaba <strong>de</strong> manera analógica y una vez en banda base se digitalizaba. Los datos digitales son enviados<br />

a una unidad <strong>de</strong> control que cuenta con un FPGA como núcleo principal, que sincroniza los datos con el<br />

controlador <strong>de</strong> radar y los envía a la PC por medio <strong>de</strong> una tarjeta <strong>de</strong> adquisición <strong>de</strong> National Instruments NI-6534.<br />

Para el sistema <strong>REX</strong> se tomó <strong>de</strong> base la arquitectura <strong>de</strong> NATALIA y se utiliza el FPGA para recibir los datos <strong>de</strong> los<br />

receptores, por medio <strong>de</strong> una lógica <strong>de</strong> multiplexado, y envía sus datos a la PC usando la NI-6534.<br />

A continuación se muestra el <strong>de</strong>sarrollo realizado para este sistema <strong>de</strong> adquisición <strong>de</strong> un radar,<br />

comenzando por una introducción al funcionamiento <strong>de</strong>l AD6620 y, luego mostrando los circuitos <strong>de</strong> cada bloque<br />

que lo componen. Dado que se trabaja con un FPGA, la <strong>de</strong>scripción lógica se realizó en VHDL, para lo cual se<br />

muestran sus máquinas y tablas <strong>de</strong> estado. En los anexos se pue<strong>de</strong> encontrar diagramas esquemáticos, diagramas<br />

<strong>de</strong> conexiones, código fuente <strong>de</strong>l software y otras informaciones útiles en este <strong>de</strong>sarrollo.<br />

2. DESARROLLO<br />

2.1 Características <strong>de</strong>l Receptor Digital AD6620.<br />

2.1.1 Descripción general <strong>de</strong>l AD6620.<br />

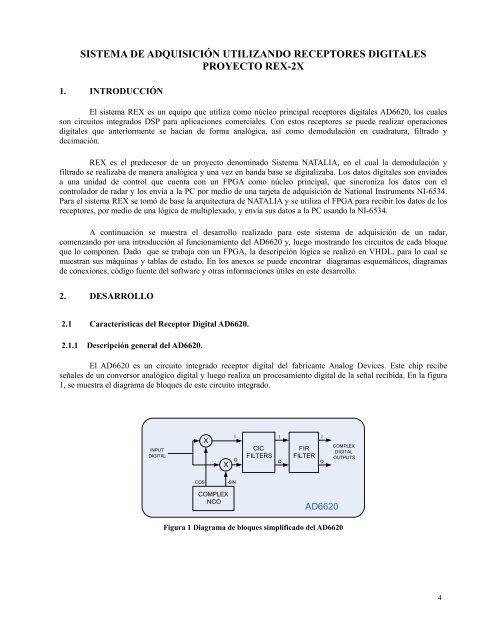

El AD6620 es un circuito integrado receptor digital <strong>de</strong>l fabricante Analog Devices. Este chip recibe<br />

señales <strong>de</strong> un conversor analógico digital y luego realiza un procesamiento digital <strong>de</strong> la señal recibida. En la figura<br />

1, se muestra el diagrama <strong>de</strong> bloques <strong>de</strong> este circuito integrado.<br />

INPUT<br />

DIGITAL<br />

X<br />

X<br />

I<br />

Q<br />

CIC<br />

FILTERS<br />

I<br />

Q<br />

FIR<br />

FILTER<br />

I<br />

Q<br />

COMPLEX<br />

DIGITAL<br />

OUTPUTS<br />

COS<br />

-SIN<br />

COMPLEX<br />

NCO<br />

AD6620<br />

Figura 1 Diagrama <strong>de</strong> bloques simplificado <strong>de</strong>l AD6620<br />

4