- Seite 1:

DISS. ETH Nr. 16370 MODULARE DREIPH

- Seite 5 und 6:

Inhaltsverzeichnis VORWORT ........

- Seite 7 und 8:

A.1 DEFINITION DES RAUMZEIGERS UND

- Seite 9:

4 BEWERTUNG UND VERGLEICH MIT DIREK

- Seite 12 und 13:

10 ausschliesslich modulare Regelun

- Seite 14 und 15:

12 The Y-Rectifier prototype is bas

- Seite 16 und 17:

14 Symbolverzeichnis ÎD Amplitude

- Seite 18 und 19:

16 Symbolverzeichnis J-C Sperrschic

- Seite 20 und 21:

18 1 Einleitung Diese Gleichrichter

- Seite 22 und 23:

20 1 Einleitung Balance zwischen Sy

- Seite 24 und 25:

22 1 Einleitung Wirkungsgrad zur Re

- Seite 26 und 27:

24 1 Einleitung bei ohmschen Netzve

- Seite 28 und 29:

26 1 Einleitung zum einen hinsichtl

- Seite 30 und 31:

28 1 Einleitung in [Cha93] wie in B

- Seite 32 und 33:

30 1 Einleitung N uN,i i=R AC + DC

- Seite 34 und 35:

32 1 Einleitung Ausgangsstufe indiv

- Seite 36 und 37:

34 1 Einleitung Ausgangsleistung vo

- Seite 38 und 39:

36 2 Delta-Rectifier 2.2 Analyse de

- Seite 40 und 41:

38 2 Delta-Rectifier Die Einschrän

- Seite 42 und 43:

40 2 Delta-Rectifier äquivalente S

- Seite 44 und 45:

42 2 Delta-Rectifier Neben Gl. (2.1

- Seite 46 und 47:

44 2 Delta-Rectifier Für die Unter

- Seite 48 und 49:

46 2 Delta-Rectifier (Das Tastverh

- Seite 50 und 51:

48 2 Delta-Rectifier Für die Träg

- Seite 52 und 53:

50 2 Delta-Rectifier [A] 3 1.5 0 -1

- Seite 54 und 55:

52 2 Delta-Rectifier In jedem Modul

- Seite 56 und 57:

54 2 Delta-Rectifier jIm α1 β6 α

- Seite 58 und 59:

56 2 Delta-Rectifier festgehalten w

- Seite 60 und 61:

58 2 Delta-Rectifier u u mij = 1−

- Seite 62 und 63:

60 2 Delta-Rectifier umgekehrt), di

- Seite 64 und 65:

62 2 Delta-Rectifier Die Integratio

- Seite 66 und 67:

64 2 Delta-Rectifier und beträgt U

- Seite 68 und 69:

66 2 Delta-Rectifier halten, wurde

- Seite 70 und 71:

68 2 Delta-Rectifier Weiters könne

- Seite 72 und 73:

70 2 Delta-Rectifier Im Normalbetri

- Seite 74 und 75:

72 2 Delta-Rectifier Wirkungsgrad,

- Seite 76 und 77:

74 2 Delta-Rectifier 2.3.3.2 Freila

- Seite 78 und 79:

76 2 Delta-Rectifier 2.3.3.4 Ausgan

- Seite 80 und 81:

78 2 Delta-Rectifier U DN block = U

- Seite 82 und 83:

80 2 Delta-Rectifier Ansatz wird f

- Seite 84 und 85:

82 2 Delta-Rectifier Induktivität

- Seite 86 und 87:

84 2 Delta-Rectifier (a) Bild 2.20.

- Seite 88 und 89:

86 2 Delta-Rectifier P 1 C min = =

- Seite 90 und 91:

88 2 Delta-Rectifier Weist die erre

- Seite 92 und 93:

90 2 Delta-Rectifier Tabelle 2.8: V

- Seite 94 und 95:

92 2 Delta-Rectifier 2.4 Systemdesi

- Seite 96 und 97:

94 2 Delta-Rectifier Details zu Rea

- Seite 98 und 99:

96 2 Delta-Rectifier 2.4.1.3.1 Anal

- Seite 100 und 101:

98 2 Delta-Rectifier ~ i I ~ iˆ ~

- Seite 102 und 103:

100 2 Delta-Rectifier 2.4.1.3.2 Dig

- Seite 104 und 105:

102 2 Delta-Rectifier stromregelung

- Seite 106 und 107:

104 2 Delta-Rectifier Reglerauslegu

- Seite 108 und 109:

106 2 Delta-Rectifier 2.4.1.5 Exper

- Seite 110 und 111:

108 2 Delta-Rectifier Es ist somit

- Seite 112 und 113:

110 2 Delta-Rectifier iD+ iD+ iN,ij

- Seite 114 und 115:

112 2 Delta-Rectifier 2.4.2 Delta-R

- Seite 116 und 117:

114 2 Delta-Rectifier Detaillierte

- Seite 118 und 119:

116 2 Delta-Rectifier Bild 2.37: Im

- Seite 120 und 121:

118 2 Delta-Rectifier Für die Ausl

- Seite 122 und 123:

120 2 Delta-Rectifier • Die Bandb

- Seite 124 und 125:

122 2 Delta-Rectifier zum gewünsch

- Seite 126 und 127:

124 2 Delta-Rectifier Tabelle 2.9:

- Seite 128 und 129:

126 2 Delta-Rectifier mij,CCM mij,D

- Seite 130 und 131:

128 2 Delta-Rectifier 2.4.2.3.3 Imp

- Seite 132 und 133:

130 2 Delta-Rectifier Tritt ein Unt

- Seite 134 und 135:

132 2 Delta-Rectifier Betrag (dB) P

- Seite 136 und 137:

134 2 Delta-Rectifier 2.4.2.4.2 Reg

- Seite 138 und 139:

136 2 Delta-Rectifier η [%] η [%]

- Seite 140 und 141:

138 2 Delta-Rectifier 2.4.2.5.1 Pha

- Seite 142 und 143:

140 2 Delta-Rectifier vorliegenden

- Seite 144 und 145:

142 2 Delta-Rectifier Bild 2.57 und

- Seite 146 und 147:

144 2 Delta-Rectifier Bild 2.59: St

- Seite 148 und 149: 146 2 Delta-Rectifier Die folgenden

- Seite 150 und 151: 148 2 Delta-Rectifier Ebenso wird a

- Seite 152 und 153: 150 2 Delta-Rectifier Ein kleiner U

- Seite 154 und 155: 152 2 Delta-Rectifier Bild 2.61: Si

- Seite 156 und 157: 154 2 Delta-Rectifier Bild 2.62: Di

- Seite 158 und 159: 156 2 Delta-Rectifier Bild 2.63: Di

- Seite 160 und 161: 158 2 Delta-Rectifier Ausregelvorga

- Seite 162 und 163: 160 2 Delta-Rectifier (u) und der E

- Seite 165 und 166: A.1 Definition des Raumzeigers und

- Seite 167: A.1 Definition des Raumzeigers und

- Seite 170 und 171: 168 3 Y-Rectifier 3.2 Analyse des G

- Seite 172 und 173: 170 3 Y-Rectifier Vernachlässigung

- Seite 174 und 175: 172 3 Y-Rectifier kann Gl.(3.7) in

- Seite 176 und 177: 174 3 Y-Rectifier jIm (111)0 (110)

- Seite 178 und 179: 176 3 Y-Rectifier • Wie gut kann

- Seite 180 und 181: 178 3 Y-Rectifier ID uN,i uN,i fS i

- Seite 182 und 183: 180 3 Y-Rectifier [V] [V] 400 200 0

- Seite 184 und 185: 182 3 Y-Rectifier resultierende Mod

- Seite 186 und 187: 184 3 Y-Rectifier kommen. Bei Verna

- Seite 188 und 189: 186 3 Y-Rectifier benachbarte Spann

- Seite 190 und 191: 188 3 Y-Rectifier 3.3 Festlegung de

- Seite 192 und 193: 190 3 Y-Rectifier C + UOY SA DA Bil

- Seite 194 und 195: 192 3 Y-Rectifier Bild 3.16: Aufbau

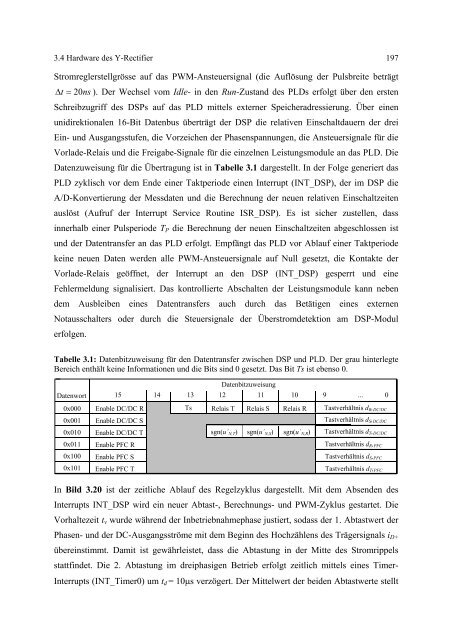

- Seite 196 und 197: 194 3 Y-Rectifier AUX+ K iDC Da DB

- Seite 200 und 201: 198 3 Y-Rectifier die Eingangsgrös

- Seite 202 und 203: 200 3 Y-Rectifier Lastaufteilung de

- Seite 204 und 205: 202 3 Y-Rectifier Mit der Vernachl

- Seite 206 und 207: 204 3 Y-Rectifier Gemeinsam mit Gl.

- Seite 208 und 209: 206 3 Y-Rectifier Für die Umsetzun

- Seite 210 und 211: 208 3 Y-Rectifier Mit der vorgestel

- Seite 212 und 213: 210 3 Y-Rectifier Gl. (3.54) einges

- Seite 214 und 215: 212 3 Y-Rectifier i u u R N S T = I

- Seite 216 und 217: 214 3 Y-Rectifier ∆Iˆ ∆Iˆ S

- Seite 218 und 219: 216 3 Y-Rectifier • die Berechnun

- Seite 220 und 221: 218 3 Y-Rectifier Aus Bild 3.25 ist

- Seite 222 und 223: 220 3 Y-Rectifier spannung. Die Bal

- Seite 224 und 225: 222 3 Y-Rectifier • Die Stellgrö

- Seite 226 und 227: 224 3 Y-Rectifier doppelter Linienf

- Seite 228 und 229: 226 3 Y-Rectifier deckt einerseits

- Seite 230 und 231: 228 3 Y-Rectifier Ohne diese Korrek

- Seite 232 und 233: 230 3 Y-Rectifier Bild 3.32: Im DSP

- Seite 234 und 235: 232 3 Y-Rectifier Bild 3.33: Eingan

- Seite 236 und 237: 234 3 Y-Rectifier Im Schwachlastbet

- Seite 238 und 239: 236 3 Y-Rectifier eine Durchtrittsf

- Seite 240 und 241: 238 3 Y-Rectifier Durch Anwendung v

- Seite 242 und 243: 240 3 Y-Rectifier Lastaufteilung du

- Seite 244 und 245: 242 3 Y-Rectifier Zur Verbesserung

- Seite 246 und 247: 244 3 Y-Rectifier 2000 1600 1200 80

- Seite 248 und 249:

246 3 Y-Rectifier ist ohne eine Las

- Seite 250 und 251:

248 3 Y-Rectifier 3.8 Initialisieru

- Seite 252 und 253:

250 3 Y-Rectifier Zwischenkreisspan

- Seite 254 und 255:

252 3 Y-Rectifier Wert ihrer beiden

- Seite 256 und 257:

254 3 Y-Rectifier Abtast-Simulation

- Seite 258 und 259:

256 3 Y-Rectifier diskontinuierlich

- Seite 260 und 261:

258 3 Y-Rectifier uout iN,S iN,R iN

- Seite 262 und 263:

260 3 Y-Rectifier Werden diese von

- Seite 264 und 265:

262 3 Y-Rectifier Bild 3.55 zeigt e

- Seite 266 und 267:

264 B.1 Überblick über Einphasen-

- Seite 268 und 269:

266 B.1 Überblick über Einphasen-

- Seite 270 und 271:

268 B.1 Überblick über Einphasen-

- Seite 272 und 273:

270 B.2 Strombelastung und Wirkungs

- Seite 274 und 275:

272 B.2 Strombelastung und Wirkungs

- Seite 276 und 277:

B.3 Globaler Effektivwert des schal

- Seite 278 und 279:

276 B.3 Globaler Effektivwert des s

- Seite 280 und 281:

278 B.3 Globaler Effektivwert des s

- Seite 282 und 283:

B.4 Dimensionierung des Leistungste

- Seite 284 und 285:

282 B.4 Dimensionierung des Leistun

- Seite 286 und 287:

284 B.4 Dimensionierung des Leistun

- Seite 288 und 289:

286 B.4 Dimensionierung des Leistun

- Seite 290 und 291:

288 B.4 Dimensionierung des Leistun

- Seite 292 und 293:

290 B.4 Dimensionierung des Leistun

- Seite 294 und 295:

292 B.4 Dimensionierung des Leistun

- Seite 296 und 297:

294 4 Bewertung und Vergleich mit d

- Seite 298 und 299:

296 4 Bewertung und Vergleich mit d

- Seite 300 und 301:

298 4 Bewertung und Vergleich mit d

- Seite 302 und 303:

300 4 Bewertung und Vergleich mit d

- Seite 304 und 305:

302 4 Bewertung und Vergleich mit d

- Seite 306 und 307:

304 4 Bewertung und Vergleich mit d

- Seite 308 und 309:

306 4 Bewertung und Vergleich mit d

- Seite 310 und 311:

308 4 Bewertung und Vergleich mit d

- Seite 312 und 313:

310 4 Bewertung und Vergleich mit d

- Seite 314 und 315:

312 4 Bewertung und Vergleich mit d

- Seite 316 und 317:

314 4 Bewertung und Vergleich mit d

- Seite 318 und 319:

316 4 Bewertung und Vergleich mit d

- Seite 320 und 321:

318 5 Zusammenfassung Im Zusammenha

- Seite 323 und 324:

Literaturverzeichnis [Bac01] BACKMA

- Seite 325 und 326:

Literaturverzeichnis 323 Stromverso

- Seite 327 und 328:

Literaturverzeichnis 325 [Kol04] KO

- Seite 329 und 330:

Literaturverzeichnis 327 Power Elec

- Seite 331:

Lebenslauf 10. 09. 1973 geboren in