Backside Circuit Edit on Device Level - New Methodologies - Imec

Backside Circuit Edit on Device Level - New Methodologies - Imec

Backside Circuit Edit on Device Level - New Methodologies - Imec

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

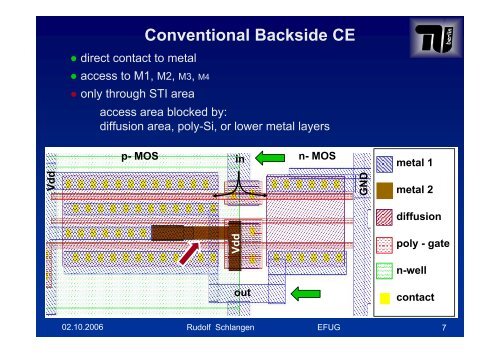

Vdd<br />

● direct c<strong>on</strong>tact to metal<br />

● access to M1, M2, M3, M4<br />

● <strong>on</strong>ly through STI area<br />

C<strong>on</strong>venti<strong>on</strong>al <str<strong>on</strong>g>Backside</str<strong>on</strong>g> CE<br />

access area blocked by:<br />

diffusi<strong>on</strong> area, poly-Si, or lower metal layers<br />

p- MOS<br />

in<br />

Vdd<br />

out<br />

n- MOS<br />

metal 1<br />

metal 2<br />

diffusi<strong>on</strong><br />

02.10.2006 Rudolf Schlangen EFUG 7<br />

GND<br />

berlin<br />

poly - gate<br />

n-well<br />

c<strong>on</strong>tact