Fast Fourier Transforms on Motorola's Digital Signal Processors

Fast Fourier Transforms on Motorola's Digital Signal Processors

Fast Fourier Transforms on Motorola's Digital Signal Processors

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

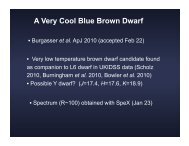

PORT<br />

A<br />

CLK<br />

4<br />

ADDRESS<br />

32<br />

C<strong>on</strong>trol<br />

19<br />

Bus<br />

C<strong>on</strong>trol<br />

32<br />

Data<br />

External<br />

Address<br />

Bus<br />

Switch<br />

Host<br />

Interface<br />

4<br />

External<br />

Data<br />

Bus<br />

Switch<br />

Clock<br />

OnCE<br />

Address<br />

Generati<strong>on</strong><br />

Unit<br />

Internal<br />

Data Bus<br />

Switch and<br />

Bit<br />

Manipulati<strong>on</strong><br />

CACHE<br />

C<strong>on</strong>trol<br />

Program<br />

RAM<br />

1024x32<br />

Unit Program C<strong>on</strong>trol Unit<br />

X Data<br />

RAM<br />

512x32<br />

1024x32<br />

Cosine<br />

ROM<br />

Y Data<br />

RAM<br />

512x32<br />

1024x32<br />

Sine<br />

ROM<br />

External<br />

Data<br />

Bus<br />

Switch<br />

Timer Timer<br />

Serial<br />

Debug<br />

Port<br />

Dual Channel<br />

DMA<br />

C<strong>on</strong>troller<br />

Boot<br />

Strap<br />

ROM<br />

64x32<br />

Program<br />

Address<br />

Generator<br />

Data ALU<br />

• IEEE Floating Point<br />

* 32x32 Integr ALU<br />

MODA/IRQA<br />

MODB/IRQB<br />

MODC/IRQC<br />

RESET<br />

Host<br />

Interface<br />

ADDRESS<br />

32<br />

C<strong>on</strong>trol<br />

19<br />

Bus<br />

C<strong>on</strong>trol<br />

4-14 MOTOROLA<br />

Y<br />

X<br />

P<br />

Program<br />

Decode<br />

C<strong>on</strong>troller<br />

D<br />

Y<br />

X<br />

P<br />

G<br />

Program<br />

Interrupt<br />

C<strong>on</strong>troller<br />

External<br />

Address<br />

Bus<br />

Switch<br />

4<br />

32<br />

Data<br />

PORT<br />

B<br />

Figure 4-6 DSP96002 Architectural Block Diagram. Two symmetric bus<br />

expansi<strong>on</strong> ports with two channel DMA c<strong>on</strong>troller that blow<br />

away the speed limit <strong>on</strong> external memory access and data I/O.