Image sensor datasheet (PDF)

Image sensor datasheet (PDF)

Image sensor datasheet (PDF)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

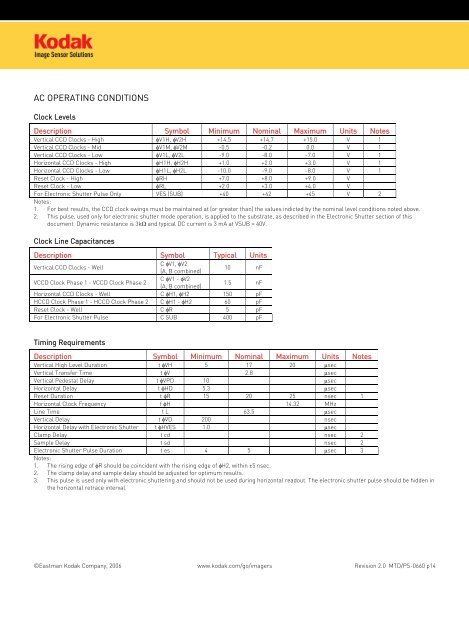

AC OPERATING CONDITIONS<br />

Clock Levels<br />

Description Symbol Minimum Nominal Maximum Units Notes<br />

Vertical CCD Clocks - High φV1H, φV2H +14.5 +14.7 +15.0 V 1<br />

Vertical CCD Clocks - Mid φV1M, φV2M -0.5 -0.2 0.0 V 1<br />

Vertical CCD Clocks - Low φV1L, φV2L -9.0 -8.0 -7.0 V 1<br />

Horizontal CCD Clocks - High φH1H, φH2H +1.0 +2.0 +3.0 V 1<br />

Horizontal CCD Clocks - Low φH1L, φH2L -10.0 -9.0 -8.0 V 1<br />

Reset Clock - High φRH +7.0 +8.0 +9.0 V<br />

Reset Clock - Low φRL +2.0 +3.0 +4.0 V<br />

For Electronic Shutter Pulse Only VES (SUB) +40 +42 +45 V 2<br />

Notes:<br />

1. For best results, the CCD clock swings must be maintained at (or greater than) the values indicted by the nominal level conditions noted above.<br />

2. This pulse, used only for electronic shutter mode operation, is applied to the substrate, as described in the Electronic Shutter section of this<br />

document. Dynamic resistance is 3kΩ and typical DC current is 3 mA at VSUB = 40V.<br />

Clock Line Capacitances<br />

Description Symbol Typical Units<br />

Vertical CCD Clocks - Well<br />

C φV1, φV2<br />

(A, B combined)<br />

10 nF<br />

VCCD Clock Phase 1 - VCCD Clock Phase 2<br />

C φV1 - φV2<br />

(A, B combined)<br />

1.5 nF<br />

Horizontal CCD Clocks - Well C φH1, φH2 150 pF<br />

HCCD Clock Phase 1 - HCCD Clock Phase 2 C φH1 - φH2 60 pF<br />

Reset Clock - Well C φR 5 pF<br />

For Electronic Shutter Pulse C SUB 400 pF<br />

Timing Requirements<br />

Description Symbol Minimum Nominal Maximum Units Notes<br />

Vertical High Level Duration t φVH 5 17 20 µsec<br />

Vertical Transfer Time t φV 2.8 µsec<br />

Vertical Pedestal Delay t φVPD 10 µsec<br />

Horizontal Delay t φHD 5.3 µsec<br />

Reset Duration t φR 15 20 25 nsec 1<br />

Horizontal Clock Frequency f φH 14.32 MHz<br />

Line Time t L 63.5 µsec<br />

Vertical Delay t φVD 200 nsec<br />

Horizontal Delay with Electronic Shutter t φHVES 1.0 µsec<br />

Clamp Delay t cd nsec 2<br />

Sample Delay t sd nsec 2<br />

Electronic Shutter Pulse Duration t es 4 5 µsec 3<br />

Notes:<br />

1. The rising edge of φR should be coincident with the rising edge of φH2, within ±5 nsec.<br />

2. The clamp delay and sample delay should be adjusted for optimum results.<br />

3. This pulse is used only with electronic shuttering and should not be used during horizontal readout. The electronic shutter pulse should be hidden in<br />

the horizontal retrace interval.<br />

©Eastman Kodak Company, 2006 www.kodak.com/go/imagers Revision 2.0 MTD/PS-0660 p14