Introduction to Cadence - UPC

Introduction to Cadence - UPC

Introduction to Cadence - UPC

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

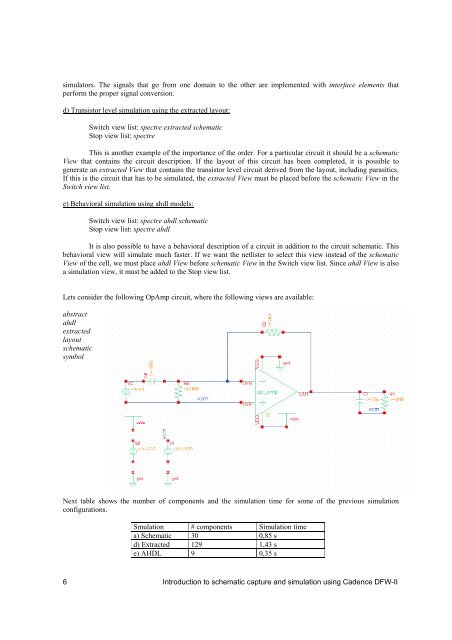

simula<strong>to</strong>rs. The signals that go from one domain <strong>to</strong> the other are implemented with interface elements thatperform the proper signal conversion.d) Transis<strong>to</strong>r level simulation using the extracted layout:Switch view list: spectre extracted schematicS<strong>to</strong>p view list: spectreThis is another example of the importance of the order. For a particular circuit it should be a schematicView that contains the circuit description. If the layout of this circuit has been completed, it is possible <strong>to</strong>generate an extracted View that contains the transis<strong>to</strong>r level circuit derived from the layout, including parasitics.If this is the circuit that has <strong>to</strong> be simulated, the extracted View must be placed before the schematic View in theSwitch view list.e) Behavioral simulation using ahdl models:Switch view list: spectre ahdl schematicS<strong>to</strong>p view list: spectre ahdlIt is also possible <strong>to</strong> have a behavioral description of a circuit in addition <strong>to</strong> the circuit schematic. Thisbehavioral view will simulate much faster. If we want the netlister <strong>to</strong> select this view instead of the schematicView of the cell, we must place ahdl View before schematic View in the Switch view list. Since ahdl View is alsoa simulation view, it must be added <strong>to</strong> the S<strong>to</strong>p view list.Lets consider the following OpAmp circuit, where the following views are available:abstractahdlextractedlayoutschematicsymbolNext table shows the number of components and the simulation time for some of the previous simulationconfigurations.Smulation # components Simulation timea) Schematic 30 0,85 sd) Extracted 129 1,43 se) AHDL 9 0,35 s6 <strong>Introduction</strong> <strong>to</strong> schematic capture and simulation using <strong>Cadence</strong> DFW-II