messtechnik & emv - EuE24.net

messtechnik & emv - EuE24.net

messtechnik & emv - EuE24.net

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

ELEKTRONIKFERTIGUNG<br />

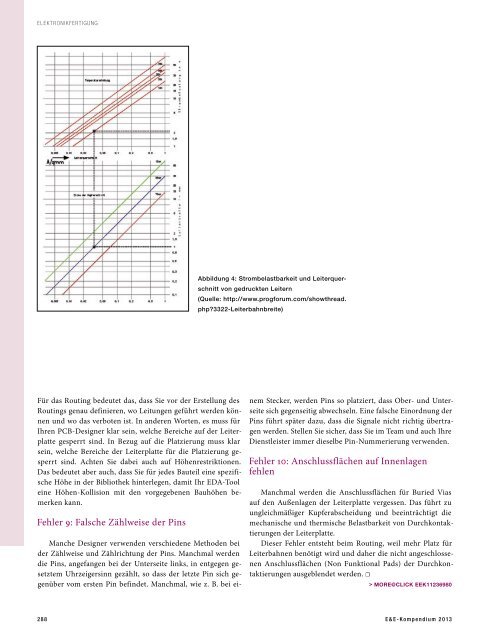

Abbildung 4: Strombelastbarkeit und Leiterquerschnitt<br />

von gedruckten Leitern<br />

(Quelle: http://www.progforum.com/showthread.<br />

php?3322-Leiterbahnbreite)<br />

Für das Routing bedeutet das, dass Sie vor der Erstellung des<br />

Routings genau definieren, wo Leitungen geführt werden können<br />

und wo das verboten ist. In anderen Worten, es muss für<br />

Ihren PCB-Designer klar sein, welche Bereiche auf der Leiterplatte<br />

gesperrt sind. In Bezug auf die Platzierung muss klar<br />

sein, welche Bereiche der Leiterplatte für die Platzierung gesperrt<br />

sind. Achten Sie dabei auch auf Höhenrestriktionen.<br />

Das bedeutet aber auch, dass Sie für jedes Bauteil eine spezifische<br />

Höhe in der Bibliothek hinterlegen, damit Ihr EDA-Tool<br />

eine Höhen-Kollision mit den vorgegebenen Bauhöhen bemerken<br />

kann.<br />

Fehler 9: Falsche Zählweise der Pins<br />

Manche Designer verwenden verschiedene Methoden bei<br />

der Zählweise und Zählrichtung der Pins. Manchmal werden<br />

die Pins, angefangen bei der Unterseite links, in entgegen gesetztem<br />

Uhrzeigersinn gezählt, so dass der letzte Pin sich gegenüber<br />

vom ersten Pin befindet. Manchmal, wie z. B. bei einem<br />

Stecker, werden Pins so platziert, dass Ober- und Unterseite<br />

sich gegenseitig abwechseln. Eine falsche Einordnung der<br />

Pins führt später dazu, dass die Signale nicht richtig übertragen<br />

werden. Stellen Sie sicher, dass Sie im Team und auch Ihre<br />

Dienstleister immer dieselbe Pin-Nummerierung verwenden.<br />

Fehler 10: Anschlussflächen auf Innenlagen<br />

fehlen<br />

Manchmal werden die Anschlussflächen für Buried Vias<br />

auf den Außenlagen der Leiterplatte vergessen. Das führt zu<br />

ungleichmäßiger Kupferabscheidung und beeinträchtigt die<br />

mechanische und thermische Belastbarkeit von Durchkontaktierungen<br />

der Leiterplatte.<br />

Dieser Fehler entsteht beim Routing, weil mehr Platz für<br />

Leiterbahnen benötigt wird und daher die nicht angeschlossenen<br />

Anschlussflächen (Non Funktional Pads) der Durchkontaktierungen<br />

ausgeblendet werden. ☐<br />

> MORE@CLICK EEK11236980<br />

2 8 8 E & E - K o m p e n d i u m 2 0 13