You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Internet Data Sheet<br />

HY[B/I]18T256[40/80/16]0B[C/F](L)<br />

256-Mbit Double-Data-Rate-Two SDRAM<br />

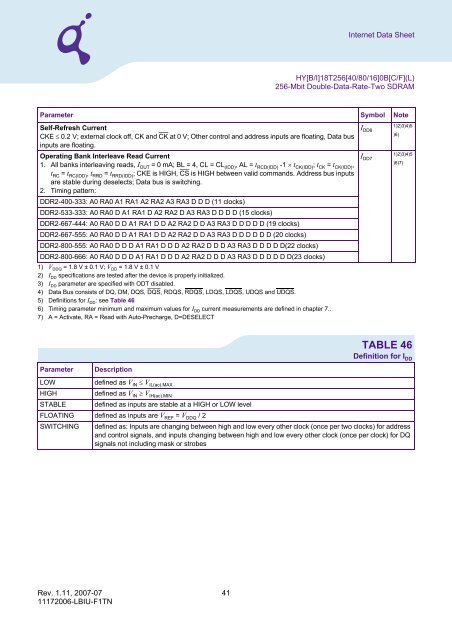

Parameter Symbol Note<br />

Self-Refresh Current<br />

CKE ≤ 0.2 V; external clock off, CK and CK at 0 V; Other control and address inputs are floating, Data bus<br />

inputs are floating.<br />

Operating Bank Interleave Read Current<br />

1. All banks interleaving reads, I OUT = 0 mA; BL = 4, CL = CL (IDD) , AL = t RCD(IDD) -1 × t CK(IDD) ; t CK = t CK(IDD) ,<br />

t RC = t RC(IDD) , t RRD = t RRD(IDD) ; CKE is HIGH, CS is HIGH between valid commands. Address bus inputs<br />

are stable during deselects; Data bus is switching.<br />

2. Timing pattern:<br />

DDR2-400-333: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D (11 clocks)<br />

DDR2-533-333: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D (15 clocks)<br />

DDR2-667-444: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D (19 clocks)<br />

DDR2-667-555: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D (20 clocks)<br />

DDR2-800-555: A0 RA0 D D D A1 RA1 D D D A2 RA2 D D D A3 RA3 D D D D D(22 clocks)<br />

DDR2-800-666: A0 RA0 D D D A1 RA1 D D D A2 RA2 D D D A3 RA3 D D D D D D(23 clocks)<br />

1) V DDQ = 1.8 V ± 0.1 V; V DD = 1.8 V ± 0.1 V<br />

2) I DD specifications are tested after the device is properly initialized.<br />

3) I DD parameter are specified with ODT disabled.<br />

4) Data Bus consists of DQ, DM, DQS, DQS, RDQS, RDQS, LDQS, LDQS, UDQS and UDQS.<br />

5) Definitions for I DD : see Table 46<br />

6) Timing parameter minimum and maximum values for I DD current measurements are defined in chapter 7..<br />

7) A = Activate, RA = Read with Auto-Precharge, D=DESELECT<br />

1)2)3)4)5<br />

I DD6<br />

)6)<br />

1)2)3)4)5<br />

I DD7<br />

)6)7)<br />

Parameter<br />

Description<br />

TABLE 46<br />

Definition for I DD<br />

LOW<br />

defined as V IN ≤ V IL(ac).MAX<br />

HIGH<br />

defined as V IN ≥ V IH(ac).MIN<br />

STABLE defined as inputs are stable at a HIGH or LOW level<br />

FLOATING defined as inputs are V REF = V DDQ / 2<br />

SWITCHING defined as: Inputs are changing between high and low every other clock (once per two clocks) for address<br />

and control signals, and inputs changing between high and low every other clock (once per clock) for DQ<br />

signals not including mask or strobes<br />

<strong>Rev</strong>. <strong>1.11</strong>, 2007-07 41<br />

11172006-LBIU-F1TN

![Internet Data Sheet HYS72T[32/64]xxxHP-[3S/3.7]-A Rev. 1.01 - UBiio](https://img.yumpu.com/50510224/1/184x260/internet-data-sheet-hys72t32-64xxxhp-3s-37-a-rev-101-ubiio.jpg?quality=85)

![Internet Data Sheet HYB18TC256[80/16]0BF Rev. 1.3 - UBiio](https://img.yumpu.com/50510226/1/184x260/internet-data-sheet-hyb18tc25680-160bf-rev-13-ubiio.jpg?quality=85)

![Internet Data Sheet HY[B/I]39SC128[800/160]FE Rev. 1.1 - UBiio](https://img.yumpu.com/31629373/1/184x260/internet-data-sheet-hyb-i39sc128800-160fe-rev-11-ubiio.jpg?quality=85)