Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

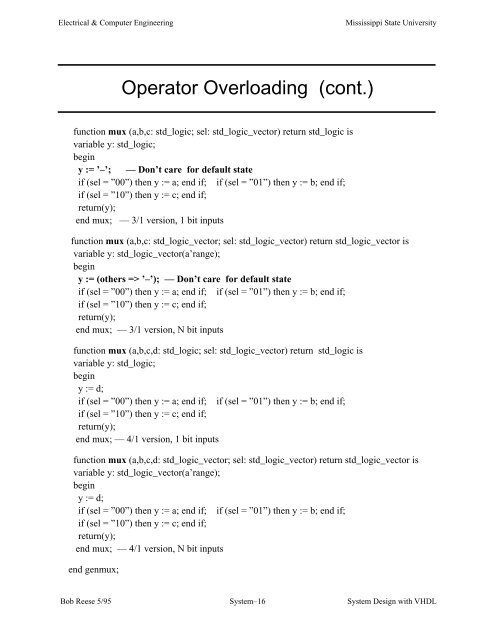

<strong>Electrical</strong> & Computer EngineeringMississippi State UniversityOperator Overloading (cont.)function mux (a,b,c: std_logic; sel: std_logic_vector) return std_logic isvariable y: std_logic;beginy := ’–’; –– Don’t care for default stateif (sel = ”00”) then y := a; end if; if (sel = ”01”) then y := b; end if;if (sel = ”10”) then y := c; end if;return(y);end mux; –– 3/1 version, 1 bit inputsfunction mux (a,b,c: std_logic_vector; sel: std_logic_vector) return std_logic_vector isvariable y: std_logic_vector(a’range);beginy := (others => ’–’); –– Don’t care for default stateif (sel = ”00”) then y := a; end if; if (sel = ”01”) then y := b; end if;if (sel = ”10”) then y := c; end if;return(y);end mux; –– 3/1 version, N bit inputsfunction mux (a,b,c,d: std_logic; sel: std_logic_vector) return std_logic isvariable y: std_logic;beginy := d;if (sel = ”00”) then y := a; end if; if (sel = ”01”) then y := b; end if;if (sel = ”10”) then y := c; end if;return(y);end mux; –– 4/1 version, 1 bit inputsfunction mux (a,b,c,d: std_logic_vector; sel: std_logic_vector) return std_logic_vector isvariable y: std_logic_vector(a’range);beginy := d;if (sel = ”00”) then y := a; end if; if (sel = ”01”) then y := b; end if;if (sel = ”10”) then y := c; end if;return(y);end mux; –– 4/1 version, N bit inputsend genmux;<strong>Bob</strong> <strong>Reese</strong> 5/95<strong>System</strong>–16<strong>System</strong> Design <strong>with</strong> <strong>VHDL</strong>