Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

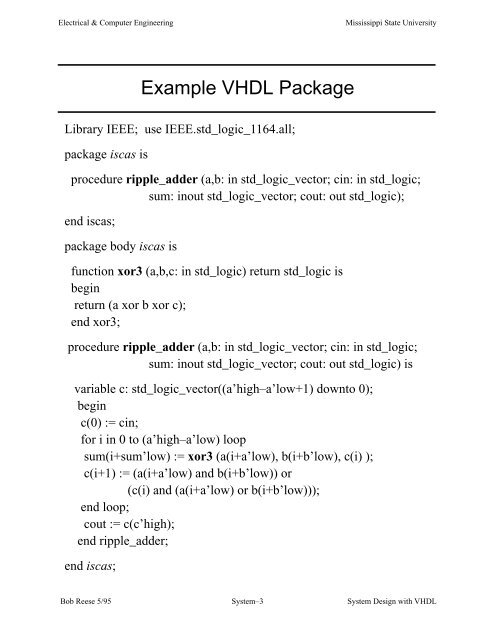

<strong>Electrical</strong> & Computer EngineeringMississippi State UniversityExample <strong>VHDL</strong> PackageLibrary IEEE; use IEEE.std_logic_1164.all;package iscas isprocedure ripple_adder (a,b: in std_logic_vector; cin: in std_logic;sum: inout std_logic_vector; cout: out std_logic);end iscas;package body iscas isfunction xor3 (a,b,c: in std_logic) return std_logic isbeginreturn (a xor b xor c);end xor3;procedure ripple_adder (a,b: in std_logic_vector; cin: in std_logic;sum: inout std_logic_vector; cout: out std_logic) isvariable c: std_logic_vector((a’high–a’low+1) downto 0);beginc(0) := cin;for i in 0 to (a’high–a’low) loopsum(i+sum’low) := xor3 (a(i+a’low), b(i+b’low), c(i) );c(i+1) := (a(i+a’low) and b(i+b’low)) or(c(i) and (a(i+a’low) or b(i+b’low)));end loop;cout := c(c’high);end ripple_adder;end iscas;<strong>Bob</strong> <strong>Reese</strong> 5/95<strong>System</strong>–3<strong>System</strong> Design <strong>with</strong> <strong>VHDL</strong>