Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

Logic Synthesis with VHDL System Synthesis Bob Reese Electrical ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

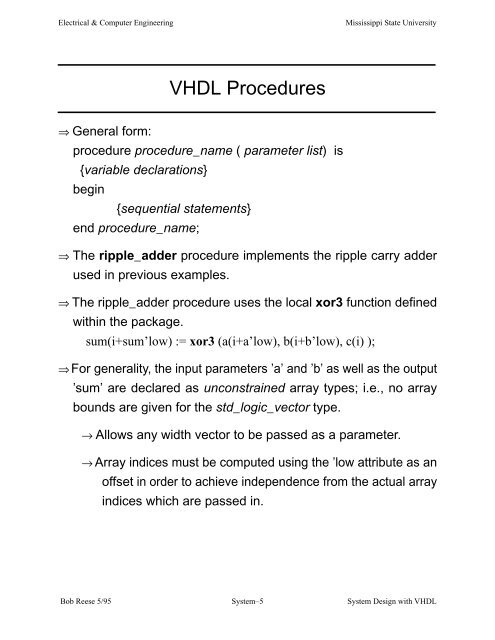

<strong>Electrical</strong> & Computer EngineeringMississippi State University<strong>VHDL</strong> Procedures⇒ General form:procedure procedure_name ( parameter list) is{variable declarations}begin{sequential statements}end procedure_name;⇒ The ripple_adder procedure implements the ripple carry adderused in previous examples.⇒ The ripple_adder procedure uses the local xor3 function defined<strong>with</strong>in the package.sum(i+sum’low) := xor3 (a(i+a’low), b(i+b’low), c(i) );⇒ For generality, the input parameters ’a’ and ’b’ as well as the output’sum’ are declared as unconstrained array types; i.e., no arraybounds are given for the std_logic_vector type.→ Allows any width vector to be passed as a parameter.→ Array indices must be computed using the ’low attribute as anoffset in order to achieve independence from the actual arrayindices which are passed in.<strong>Bob</strong> <strong>Reese</strong> 5/95<strong>System</strong>–5<strong>System</strong> Design <strong>with</strong> <strong>VHDL</strong>