ECEN 454 Digital Integrated Circuit Design Lab9

ECEN 454 Digital Integrated Circuit Design Lab9

ECEN 454 Digital Integrated Circuit Design Lab9

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

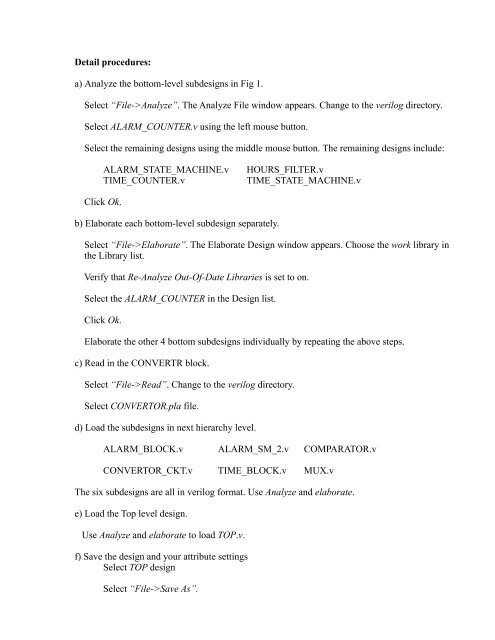

Detail procedures:a) Analyze the bottom-level subdesigns in Fig 1.Select “File->Analyze”. The Analyze File window appears. Change to the verilog directory.Select ALARM_COUNTER.v using the left mouse button.Select the remaining designs using the middle mouse button. The remaining designs include:ALARM_STATE_MACHINE.vTIME_COUNTER.vHOURS_FILTER.vTIME_STATE_MACHINE.vClick Ok.b) Elaborate each bottom-level subdesign separately.Select “File->Elaborate”. The Elaborate <strong>Design</strong> window appears. Choose the work library inthe Library list.Verify that Re-Analyze Out-Of-Date Libraries is set to on.Select the ALARM_COUNTER in the <strong>Design</strong> list.Click Ok.Elaborate the other 4 bottom subdesigns individually by repeating the above steps.c) Read in the CONVERTR block.Select “File->Read”. Change to the verilog directory.Select CONVERTOR.pla file.d) Load the subdesigns in next hierarchy level.ALARM_BLOCK.v ALARM_SM_2.v COMPARATOR.vCONVERTOR_CKT.v TIME_BLOCK.v MUX.vThe six subdesigns are all in verilog format. Use Analyze and elaborate.e) Load the Top level design.Use Analyze and elaborate to load TOP.v.f) Save the design and your attribute settingsSelect TOP designSelect “File->Save As”.