CS5531/32/33/34 - Eshop-Rychle.cz

CS5531/32/33/34 - Eshop-Rychle.cz

CS5531/32/33/34 - Eshop-Rychle.cz

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

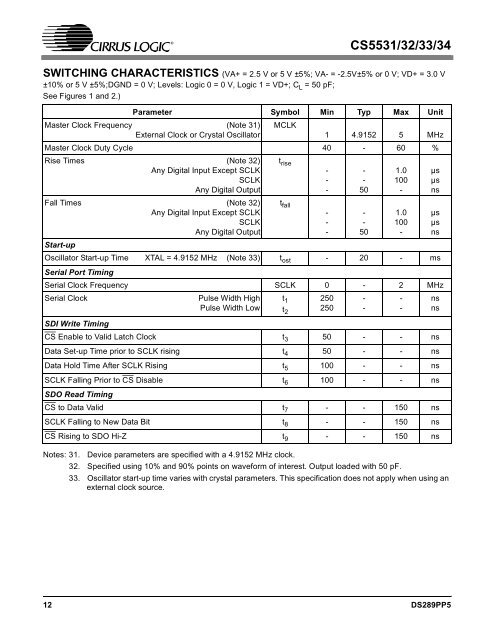

<strong>CS5531</strong>/<strong>32</strong>/<strong>33</strong>/<strong>34</strong>SWITCHING CHARACTERISTICS (VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V±10% or 5 V ±5%;DGND = 0 V; Levels: Logic 0 = 0 V, Logic 1 = VD+; C L =50pF;See Figures 1 and 2.)Parameter Symbol Min Typ Max UnitMaster Clock Frequency (Note 31) MCLKExternal Clock or Crystal Oscillator1 4.9152 5 MHzMaster Clock Duty Cycle 40 - 60 %Rise Times (Note <strong>32</strong>)Any Digital Input Except SCLKSCLKAny Digital OutputFall Times (Note <strong>32</strong>)Any Digital Input Except SCLKSCLKAny Digital OutputStart-upt rise---t fall---Oscillator Start-up Time XTAL = 4.9152 MHz (Note <strong>33</strong>) t ost - 20 - msSerial Port TimingSerial Clock Frequency SCLK 0 - 2 MHzSerial ClockPulse Width High t 1- - nsPulse Width Low t 2250 - - nsSDI Write TimingCS Enable to Valid Latch Clock t 3 50 - - nsData Set-up Time prior to SCLK rising t 4 50 - - nsData Hold Time After SCLK Rising t 5 100 - - nsSCLK Falling Prior to CS Disable t 6 100 - - nsSDO Read TimingCS to Data Valid t 7 - - 150 nsSCLK Falling to New Data Bit t 8 - - 150 nsCS Rising to SDO Hi-Z t 9 - - 150 nsNotes: 31. Device parameters are specified with a 4.9152 MHz clock.<strong>32</strong>. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.<strong>33</strong>. Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.--50--501.0100-1.0100-µsµsnsµsµsns12 DS289PP5