CS5531/32/33/34 - Eshop-Rychle.cz

CS5531/32/33/34 - Eshop-Rychle.cz

CS5531/32/33/34 - Eshop-Rychle.cz

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

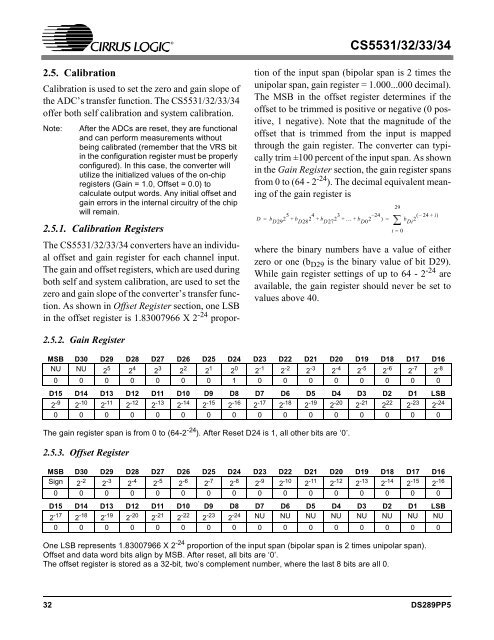

<strong>CS5531</strong>/<strong>32</strong>/<strong>33</strong>/<strong>34</strong>2.5. CalibrationCalibration is used to set the zero and gain slope ofthe ADC’s transfer function. The <strong>CS5531</strong>/<strong>32</strong>/<strong>33</strong>/<strong>34</strong>offer both self calibration and system calibration.Note:After the ADCs are reset, they are functionaland can perform measurements withoutbeing calibrated (remember that the VRS bitin the configuration register must be properlyconfigured). In this case, the converter willutilize the initialized values of the on-chipregisters (Gain = 1.0, Offset = 0.0) tocalculate output words. Any initial offset andgain errors in the internal circuitry of the chipwill remain.2.5.1. Calibration RegistersThe <strong>CS5531</strong>/<strong>32</strong>/<strong>33</strong>/<strong>34</strong> converters have an individualoffset and gain register for each channel input.The gain and offset registers, which are used duringboth self and system calibration, are used to set thezero and gain slope of the converter’s transfer function.As shown in Offset Register section, one LSBin the offset register is 1.83007966 X 2 -24 proportionof the input span (bipolar span is 2 times theunipolar span, gain register = 1.000...000 decimal).The MSB in the offset register determines if theoffset to be trimmed is positive or negative (0 positive,1 negative). Note that the magnitude of theoffset that is trimmed from the input is mappedthrough the gain register. The converter can typicallytrim ±100 percent of the input span. As shownin the Gain Register section, the gain register spansfrom 0 to (64 - 2 -24 ). The decimal equivalent meaningof the gain register is29D b D292 5 + b D282 4 + b D272 3 + … + b D02 – 24(– 24 + i)= ) = b Di2i = 0where the binary numbers have a value of eitherzero or one (b D29 is the binary value of bit D29).While gain register settings of up to 64 - 2 -24 areavailable, the gain register should never be set tovalues above 40.∑2.5.2. Gain RegisterMSB D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16NU NU 2 5 2 4 2 3 2 2 2 1 2 0 2 -1 2 -2 2 -3 2 -4 2 -5 2 -6 2 -7 2 -80 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 LSB2 -9 2 -10 2 -11 2 -12 2 -13 2 -14 2 -15 2 -16 2 -17 2 -18 2 -19 2 -20 2 -21 2 22 2 -23 2 -240 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0The gain register span is from 0 to (64-2 -24 ). After Reset D24 is 1, all other bits are ‘0’.2.5.3. Offset RegisterMSB D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16Sign 2 -2 2 -3 2 -4 2 -5 2 -6 2 -7 2 -8 2 -9 2 -10 2 -11 2 -12 2 -13 2 -14 2 -15 2 -160 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 LSB2 -17 2 -18 2 -19 2 -20 2 -21 2 -22 2 -23 2 -24 NU NU NU NU NU NU NU NU0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0One LSB represents 1.83007966 X 2 -24 proportion of the input span (bipolar span is 2 times unipolar span).Offset and data word bits align by MSB. After reset, all bits are ‘0’.The offset register is stored as a <strong>32</strong>-bit, two’s complement number, where the last 8 bits are all 0.<strong>32</strong> DS289PP5