THE OCULUS-F/64 FRAME GRABBER User's Manual

THE OCULUS-F/64 FRAME GRABBER User's Manual

THE OCULUS-F/64 FRAME GRABBER User's Manual

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

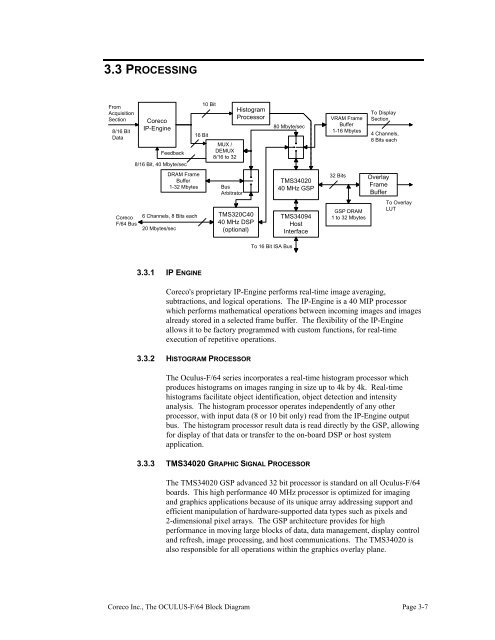

3.3 PROCESSING<br />

From<br />

Acquisition<br />

Section<br />

8/16 Bit<br />

Data<br />

Coreco<br />

F/<strong>64</strong> Bus<br />

Coreco<br />

IP-Engine<br />

Feedback<br />

8/16 Bit, 40 Mbyte/sec<br />

DRAM Frame<br />

Buffer<br />

1-32 Mbytes<br />

6 Channels, 8 Bits each<br />

20 Mbytes/sec<br />

16 Bit<br />

3.3.1 IP ENGINE<br />

10 Bit<br />

MUX /<br />

DEMUX<br />

8/16 to 32<br />

Bus<br />

Arbitrator<br />

Histogram<br />

Processor<br />

TMS320C40<br />

40 MHz DSP<br />

(optional)<br />

80 Mbyte/sec<br />

To 16 Bit ISA Bus<br />

TMS34020<br />

40 MHz GSP<br />

TMS34094<br />

Host<br />

Interface<br />

VRAM Frame<br />

Buffer<br />

1-16 Mbytes<br />

To Display<br />

Section<br />

4 Channels,<br />

8 Bits each<br />

To Overlay<br />

LUT<br />

Coreco Inc., The <strong>OCULUS</strong>-F/<strong>64</strong> Block Diagram Page 3-7<br />

32 Bits<br />

GSP DRAM<br />

1 to 32 Mbytes<br />

Overlay<br />

Frame<br />

Buffer<br />

Coreco's proprietary IP-Engine performs real-time image averaging,<br />

subtractions, and logical operations. The IP-Engine is a 40 MIP processor<br />

which performs mathematical operations between incoming images and images<br />

already stored in a selected frame buffer. The flexibility of the IP-Engine<br />

allows it to be factory programmed with custom functions, for real-time<br />

execution of repetitive operations.<br />

3.3.2 HISTOGRAM PROCESSOR<br />

The Oculus-F/<strong>64</strong> series incorporates a real-time histogram processor which<br />

produces histograms on images ranging in size up to 4k by 4k. Real-time<br />

histograms facilitate object identification, object detection and intensity<br />

analysis. The histogram processor operates independently of any other<br />

processor, with input data (8 or 10 bit only) read from the IP-Engine output<br />

bus. The histogram processor result data is read directly by the GSP, allowing<br />

for display of that data or transfer to the on-board DSP or host system<br />

application.<br />

3.3.3 TMS34020 GRAPHIC SIGNAL PROCESSOR<br />

The TMS34020 GSP advanced 32 bit processor is standard on all Oculus-F/<strong>64</strong><br />

boards. This high performance 40 MHz processor is optimized for imaging<br />

and graphics applications because of its unique array addressing support and<br />

efficient manipulation of hardware-supported data types such as pixels and<br />

2-dimensional pixel arrays. The GSP architecture provides for high<br />

performance in moving large blocks of data, data management, display control<br />

and refresh, image processing, and host communications. The TMS34020 is<br />

also responsible for all operations within the graphics overlay plane.