- Page 1 and 2:

i

- Page 3 and 4:

DISKLAIMER (DISCLAIMER) Penerbit ti

- Page 5 and 6:

PROSES PEMBELAJARAN KURIKULUM 2013

- Page 7 and 8:

GLOSARIUM 802.11 802.11 merupakan s

- Page 9 and 10:

LAN MAC address Local Area Network

- Page 11 and 12:

DAFTAR ISI DISKLAIMER (DISCLAIMER)

- Page 13 and 14:

BAB I. SISTEM KOMUNIKASI DATA 1.1 P

- Page 15 and 16:

1.2 APLIKASI KOMUNIKASI Komunikasi

- Page 17 and 18:

(http://www.witke.com/witke/) Gamba

- Page 19 and 20:

proses pengalihan informasi melalui

- Page 21 and 22:

d. Transport Layer Transport Layer

- Page 23 and 24:

a.Unipolar Line Coding Kode ini men

- Page 25 and 26:

tegangan positip, dan sinyal harus

- Page 27 and 28:

unipolar RZ (Return Zero), dari bin

- Page 29 and 30:

Gambar 1.13. Diagram pulsa pengkode

- Page 31 and 32:

Kode ASCII yang terdiri dari 7 bit

- Page 33 and 34:

software maupun secara hardware mem

- Page 35 and 36:

Terlebih pada transmisi data serial

- Page 37 and 38:

i. Kode Koreksi Error Kode Hamming

- Page 39 and 40:

. Penyelesaian untuk data = 011 Kod

- Page 41 and 42:

Penentuan bit kode Hamming untuk pe

- Page 43 and 44:

Gambar 1.19 merupakan frame pesan H

- Page 45 and 46:

SOAL DAN PERTANYAAN: 1. Mengapa dal

- Page 47 and 48:

17. Jelaskan pendapat anda tentang

- Page 49 and 50:

DESKRIPSI MATERI PEMBELAJARAN Kebut

- Page 51 and 52:

Secara umum, jaringan mempunyai beb

- Page 53 and 54:

RAM dan ruang penyimpan lebih besar

- Page 55 and 56:

lain. Sebagian hub -- terutama dari

- Page 57 and 58:

Gambar 2.5. Bridge sebagai penghubu

- Page 59 and 60:

jaringan, protocol, dan seberapa be

- Page 61 and 62:

Gambar 2.8. Dua Jenis Konfigurasi K

- Page 63 and 64:

‣ Gelombang Mikro (Microwave) Med

- Page 65 and 66:

Gambar 2.13. Topologi Linear Bus

- Page 67 and 68:

dengan kabel utama (backbone cable)

- Page 69 and 70:

Protokol yang mendukung berbagai pe

- Page 71 and 72:

Umumnya digunakan untuk penghubung

- Page 73 and 74:

d. Kesimpulan Protocol Kable Kecepa

- Page 75 and 76:

saluran bebas. Besar kemungkinannya

- Page 77 and 78:

disk drive, dan semua komputer yang

- Page 79 and 80:

c. Menginstal DHCP Server Cara meng

- Page 81 and 82:

Pada gambar 2.20, diambil contoh al

- Page 83 and 84:

power work group 3.1sampai versi te

- Page 85 and 86:

‣ Menginstal Network Adapter Hamp

- Page 87 and 88:

Bila mutlak tidak akan menggunakan

- Page 89 and 90:

Setiap komputer pada satu jaringan,

- Page 91 and 92:

2.7 KONEKSI ANTAR NETWORK a. Perala

- Page 93 and 94:

Contohnya, ketika jalur optimum saa

- Page 95 and 96:

Sistem jaringan ini dapat menggunak

- Page 97 and 98:

Beberapa contoh packet-switching ad

- Page 99 and 100:

Gambar 2.35. CSU/DSU terletak antar

- Page 101 and 102:

‣ Kerugian TCP/IP Karena adanya

- Page 103 and 104:

Prinsip kerja dari TCP berdasarkan

- Page 105 and 106:

Standar (default) Subnet Mask adala

- Page 107 and 108:

informasi dalam penggunaan perintah

- Page 109 and 110: Gambar 2.39. Digital Multimeter dan

- Page 111 and 112: 8. Pelajari blok diagram berikut de

- Page 113 and 114: c. Kabel Coaxial d. Fiber Optic Cab

- Page 115 and 116: 15. Jelaskan pertimbangan dalam mem

- Page 117 and 118: BAB III. SISTEM PROTOKOL JARINGAN 3

- Page 119 and 120: akhir dari setiap rangkaian data da

- Page 121 and 122: Gambar 3.1. Kode balik dari penerim

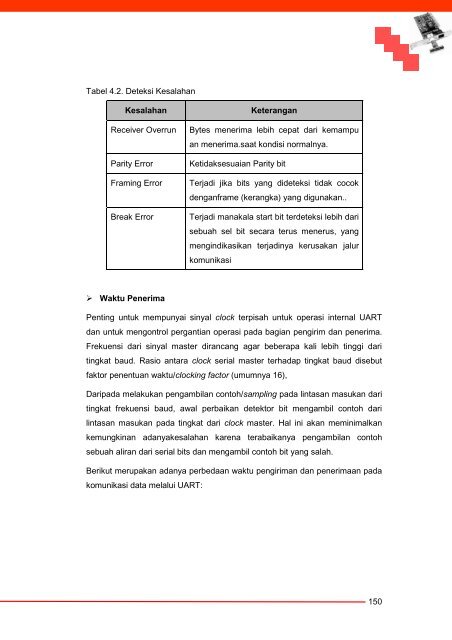

- Page 123 and 124: Jika penerima menemui sebuah Kesala

- Page 125 and 126: yang lebih efisien yang menomori se

- Page 127 and 128: . Tipe dan Frame Format HDLC ‣ Ke

- Page 129 and 130: Pada mode NRM, jika simpul sekunder

- Page 131 and 132: dengan yang ada pada paket, penerim

- Page 133 and 134: Sebuah tanda NAK berarti transmisi

- Page 135 and 136: Teknik berhenti dan tunggu digunaka

- Page 137 and 138: Keterangan: MARK LEN SEQ TYPE DATA

- Page 139 and 140: SOAL DAN TUGAS: 1. Dalam sebuah pro

- Page 141 and 142: BAB IV. KOMUNIKASI DATA DI INDUSTRI

- Page 143 and 144: % AD 00 Data CS CR Awal Alamat Peri

- Page 145 and 146: ‣ Jaringan Komunikasi EIA EIA-232

- Page 147 and 148: Perintah ini membaca dari pengirim

- Page 149 and 150: Protokol transmisi Modbus dikembang

- Page 151 and 152: Perintah kontrol spiral (Coil contr

- Page 153 and 154: 2) Penyelarasan (Synchronisation) U

- Page 155 and 156: tunggal Coils 00001 to 09999 0 to 9

- Page 157 and 158: Menentukan parity dan menambahkan s

- Page 159: Ketika semua bits telah dikirimkan

- Page 163 and 164: . Komunikasi Data Melalui RS232 Pad

- Page 165 and 166: Gambar 4.12. Koneksi 2 komputer mel

- Page 167 and 168: contoh untuk keperluan khusus UART

- Page 169 and 170: Data Terminal Ready (DTR)berfungsi

- Page 171 and 172: Pada protokol RS232 perlu dilakukan

- Page 173 and 174: untuk digunakan sebagai pelindung t

- Page 175 and 176: Gambar 4.21. Lebar pita pada jalur

- Page 177 and 178: Gambar 4.23. Pengiriman Secara Blok

- Page 179 and 180: 6) Modem yang memulai inisiatif mem

- Page 181 and 182: Penentu tingkat sinyal data Pendet

- Page 183 and 184: 2) Distorsi penundaan/ envelope del

- Page 185 and 186: endah, terdapat kesulitan membedaka

- Page 187 and 188: Gambar 4.29. Direct Frequency Modul

- Page 189 and 190: Dibit Phase Shift 00 0 o 01 90 o 10

- Page 191 and 192: Di mana: P 1 = b 1 XORb 0 = 1XOR0 =

- Page 193 and 194: Penyetara/Equaliser, penyetara memi

- Page 195 and 196: 1) mode commands 2) numeric registe

- Page 197 and 198: Kode Keterangan D, Perintah pemangg

- Page 199 and 200: Kode V,V0 Keterangan Kode hasil Num

- Page 201 and 202: S10 S11 Batas waktu untuk memutusk

- Page 203 and 204: S28 S29 Hitung hubungan yang gaga

- Page 205 and 206: Tabel 4.6. Efisiensi Aplikasi MNP K

- Page 207 and 208: Kode frekuensi adaptif Dalam kode f

- Page 209 and 210: 6) Tempatkan sebuah 1 pada cabang y

- Page 211 and 212:

Tipe Modem Tingkat TS /,S Mode Modu

- Page 213 and 214:

. Tes Lingkaran balik/Loop Back Set

- Page 215 and 216:

‣ Koreksi/deteksi Kesalahan, meka

- Page 217 and 218:

Gambar 4.38 berikut ini menunjukkan

- Page 219 and 220:

UDP menyediakan layanan satu ke sat

- Page 221 and 222:

ini dari Kesalahan. Pengesahan dari

- Page 223 and 224:

‣ ARP Ketika paket IP dikirimkan

- Page 225 and 226:

Destination Unreachable (Protokol U

- Page 227 and 228:

Pesan IGMP terdiri dari dua bentuk:

- Page 229 and 230:

Assigned Numbers Authority (IANA).

- Page 231 and 232:

‣ Interface Aplikasi TCP/IP Agar

- Page 233 and 234:

NetBIOS menyediakan perintah dan du

- Page 235 and 236:

Resolusi Nama Ketika IP dirancang u

- Page 237 and 238:

Dibawah level domain top-level adal

- Page 239 and 240:

Pengantaran Langsung terjadi saat s

- Page 241 and 242:

SOAL DAN TUGAS: 1. Sebutkan dan jel

- Page 243 and 244:

? 1 [SP] B A D [SP] C H E C K S U M

- Page 245 and 246:

10. Lengkapi tabel deteksi Kesalaha

- Page 247 and 248:

14. Buatlah koneksi seperti gambar

- Page 249:

238