Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

zove magistrala. Za konstrukciju magistrale koristi se trostatički bafer koja, kao elektronska<br />

komponenta, može imati tri različita stanja na izlazu: 0, 1 i Z. Vrednost Z predstavlja stanje visoke<br />

impedanse, koje se kod svih praktičnih primena može smatrati prekidom veze.<br />

(a)<br />

(b)<br />

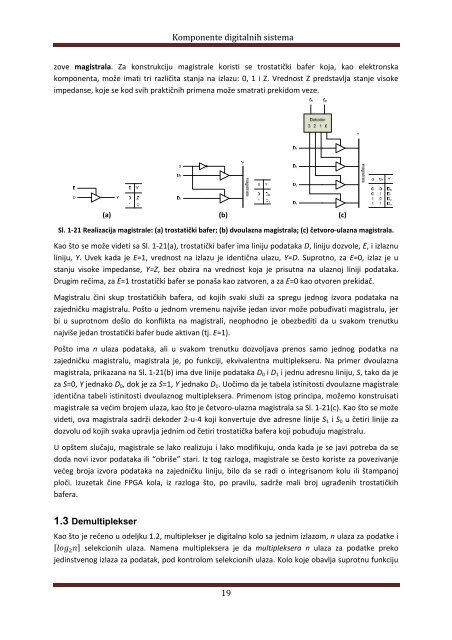

Sl. 1‐21 Realizacija magistrale: (a) trostatički bafer; (b) dvoulazna magistrala; (c) četvoro‐ulazna magistrala.<br />

Kao što se može videti sa Sl. 1‐21(a), trostatički bafer ima liniju podataka D, liniju dozvole, E, i izlaznu<br />

liniju, Y. Uvek kada je E=1, vrednost na izlazu je identična ulazu, Y=D. Suprotno, za E=0, izlaz je u<br />

stanju visoke impedanse, Y=Z, bez obzira na vrednost koja je prisutna na ulaznoj liniji podataka.<br />

Drugim rečima, za E=1 trostatički bafer se ponaša kao zatvoren, a za E=0 kao otvoren prekidač.<br />

Magistralu čini skup trostatičkih bafera, od kojih svaki služi za spregu jednog izvora podataka na<br />

zajedničku magistralu. Pošto u jednom vremenu najviše jedan izvor može pobuđivati magistralu, jer<br />

bi u suprotnom došlo do konflikta na magistrali, neophodno je obezbediti da u svakom trenutku<br />

najviše jedan trostatički bafer bude aktivan (tj. E=1).<br />

Pošto ima n ulaza podataka, ali u svakom trenutku dozvoljava prenos samo jednog podatka na<br />

zajedničku magistralu, magistrala je, po funkciji, ekvivalentna multiplekseru. Na primer dvoulazna<br />

magistrala, prikazana na Sl. 1‐21(b) ima dve linije podataka D0 i D1 i jednu adresnu liniju, S, tako da je<br />

za S=0, Y jednako D0, dok je za S=1, Y jednako D1. Uočimo da je tabela istinitosti dvoulazne magistrale<br />

identična tabeli istinitosti dvoulaznog multipleksera. Primenom istog principa, možemo konstruisati<br />

magistrale sa većim brojem ulaza, kao što je četvoro‐ulazna magistrala sa Sl. 1‐21(c). Kao što se može<br />

videti, ova magistrala sadrži dekoder 2‐u‐4 koji konvertuje dve adresne linije S1 i S0 u četiri linije za<br />

dozvolu od kojih svaka upravlja jednim od četiri trostatička bafera koji pobuđuju magistralu.<br />

U opštem slučaju, magistrale se lako realizuju i lako modifikuju, onda kada je se javi potreba da se<br />

doda novi izvor podataka ili “obriše” stari. Iz tog razloga, magistrale se često koriste za povezivanje<br />

većeg broja izvora podataka na zajedničku liniju, bilo da se radi o integrisanom kolu ili štampanoj<br />

ploči. Izuzetak čine FPGA kola, iz razloga što, po pravilu, sadrže mali broj ugrađenih trostatičkih<br />

bafera.<br />

1.3 Demultiplekser<br />

Kao što je rečeno u odeljku 1.2, multiplekser je digitalno kolo sa jednim izlazom, n ulaza za podatke i<br />

selekcionih ulaza. Namena multipleksera je da multipleksera n ulaza za podatke preko<br />

jedinstvenog izlaza za podatak, pod kontrolom selekcionih ulaza. Kolo koje obavlja suprotnu funkciju<br />

19<br />

(c)