Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

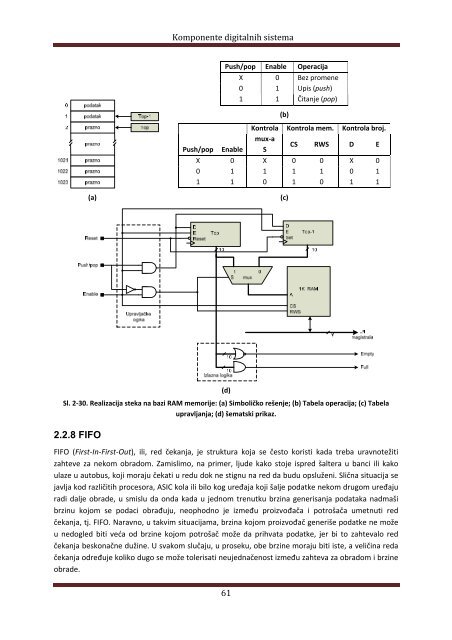

(a)<br />

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

Push/pop Enable<br />

Push/pop Enable Operacija<br />

61<br />

X 0 Bez promene<br />

0 1 Upis (push)<br />

1 1 Čitanje (pop)<br />

Kontrola<br />

mux‐a<br />

S<br />

(b)<br />

(c)<br />

Kontrola mem. Kontrola broj.<br />

CS RWS D E<br />

X 0 X 0 0 X 0<br />

0 1 1 1 1 0 1<br />

1 1 0 1 0 1 1<br />

(d)<br />

Sl. 2‐30. Realizacija steka na bazi RAM memorije: (a) Simboličko rešenje; (b) Tabela operacija; (c) Tabela<br />

upravljanja; (d) šematski prikaz.<br />

2.2.8 FIFO<br />

FIFO (First‐In‐First‐Out), ili, red čekanja, je struktura koja se često koristi kada treba uravnotežiti<br />

zahteve za nekom obradom. Zamislimo, na primer, ljude kako stoje ispred šaltera u banci ili kako<br />

ulaze u autobus, koji moraju čekati u redu dok ne stignu na red da budu opsluženi. Slična situacija se<br />

javlja kod različitih procesora, ASIC kola ili bilo kog uređaja koji šalje podatke nekom drugom uređaju<br />

radi dalje obrade, u smislu da onda kada u jednom trenutku brzina generisanja podataka nadmaši<br />

brzinu kojom se podaci obrađuju, neophodno je između proizvođača i potrošača umetnuti red<br />

čekanja, tj. FIFO. Naravno, u takvim situacijama, brzina kojom proizvođač generiše podatke ne može<br />

u nedogled biti veća od brzine kojom potrošač može da prihvata podatke, jer bi to zahtevalo red<br />

čekanja beskonačne dužine. U svakom slučaju, u proseku, obe brzine moraju biti iste, a veličina reda<br />

čekanja određuje koliko dugo se može tolerisati neujednačenost između zahteva za obradom i brzine<br />

obrade.