Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

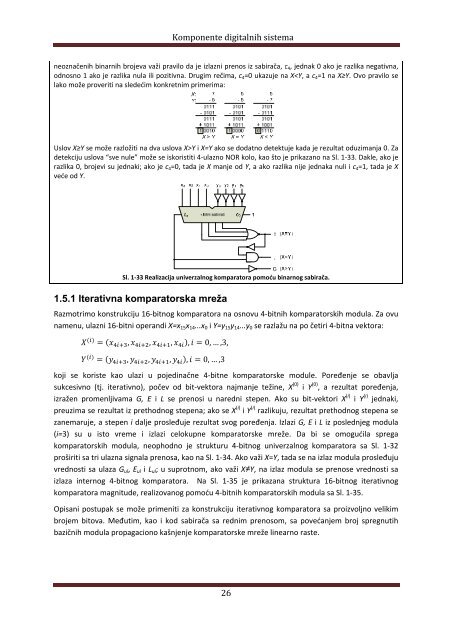

neoznačenih binarnih brojeva važi pravilo da je izlazni prenos iz sabirača, c4, jednak 0 ako je razlika negativna,<br />

odnosno 1 ako je razlika nula ili pozitivna. Drugim rečima, c4=0 ukazuje na XY i X=Y ako se dodatno detektuje kada je rezultat oduzimanja 0. Za<br />

detekciju uslova “sve nule” može se iskoristiti 4‐ulazno NOR kolo, kao što je prikazano na Sl. 1‐33. Dakle, ako je<br />

razlika 0, brojevi su jednaki; ako je c4=0, tada je X manje od Y, a ako razlika nije jednaka nuli i c4=1, tada je X<br />

veće od Y.<br />

Sl. 1‐33 Realizacija univerzalnog komparatora pomoću binarnog sabirača.<br />

1.5.1 Iterativna komparatorska mreža<br />

Razmotrimo konstrukciju 16‐bitnog komparatora na osnovu 4‐bitnih komparatorskih modula. Za ovu<br />

namenu, ulazni 16‐bitni operandi X=x15x14...x0 i Y=y15y14...y0 se razlažu na po četiri 4‐bitna vektora:<br />

, , , , 0,…,3,<br />

, , , , 0,…,3<br />

koji se koriste kao ulazi u pojedinačne 4‐bitne komparatorske module. Poređenje se obavlja<br />

sukcesivno (tj. iterativno), počev od bit‐vektora najmanje težine, X (0) i Y (0) , a rezultat poređenja,<br />

izražen promenljivama G, E i L se prenosi u naredni stepen. Ako su bit‐vektori X (i) i Y (i) jednaki,<br />

preuzima se rezultat iz prethodnog stepena; ako se X (i) i Y (i) razlikuju, rezultat prethodnog stepena se<br />

zanemaruje, a stepen i dalje prosleđuje rezultat svog poređenja. Izlazi G, E i L iz poslednjeg modula<br />

(i=3) su u isto vreme i izlazi celokupne komparatorske mreže. Da bi se omogućila sprega<br />

komparatorskih modula, neophodno je strukturu 4‐bitnog univerzalnog komparatora sa Sl. 1‐32<br />

proširiti sa tri ulazna signala prenosa, kao na Sl. 1‐34. Ako važi X=Y, tada se na izlaz modula prosleđuju<br />

vrednosti sa ulaza Gul, Eul i Lul; u suprotnom, ako važi X≠Y, na izlaz modula se prenose vrednosti sa<br />

izlaza internog 4‐bitnog komparatora. Na Sl. 1‐35 je prikazana struktura 16‐bitnog iterativnog<br />

komparatora magnitude, realizovanog pomoću 4‐bitnih komparatorskih modula sa Sl. 1‐35.<br />

Opisani postupak se može primeniti za konstrukciju iterativnog komparatora sa proizvoljno velikim<br />

brojem bitova. Međutim, kao i kod sabirača sa rednim prenosom, sa povećanjem broj spregnutih<br />

bazičnih modula propagaciono kašnjenje komparatorske mreže linearno raste.<br />

26