Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

(a)<br />

(b)<br />

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

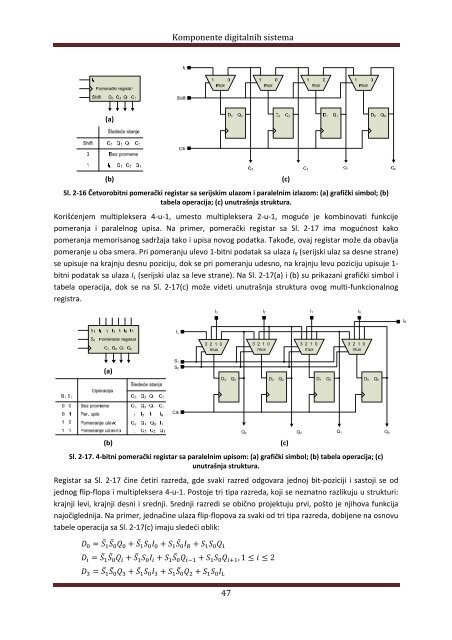

Sl. 2‐16 Četvorobitni pomerački registar sa serijskim ulazom i paralelnim izlazom: (a) grafički simbol; (b)<br />

tabela operacija; (c) unutrašnja struktura.<br />

Korišćenjem multipleksera 4‐u‐1, umesto multipleksera 2‐u‐1, moguće je kombinovati funkcije<br />

pomeranja i paralelnog upisa. Na primer, pomerački registar sa Sl. 2‐17 ima mogućnost kako<br />

pomeranja memorisanog sadržaja tako i upisa novog podatka. Takođe, ovaj registar može da obavlja<br />

pomeranje u oba smera. Pri pomeranju ulevo 1‐bitni podatak sa ulaza IR (serijski ulaz sa desne strane)<br />

se upisuje na krajnju desnu poziciju, dok se pri pomeranju udesno, na krajnju levu poziciju upisuje 1‐<br />

bitni podatak sa ulaza IL (serijski ulaz sa leve strane). Na Sl. 2‐17(a) i (b) su prikazani grafički simbol i<br />

tabela operacija, dok se na Sl. 2‐17(c) može videti unutrašnja struktura ovog multi‐funkcionalnog<br />

registra.<br />

(a)<br />

IL<br />

S1<br />

S0<br />

Clk<br />

3 2 1 0<br />

mux<br />

(b) (c)<br />

Sl. 2‐17. 4‐bitni pomerački registar sa paralelnim upisom: (a) grafički simbol; (b) tabela operacija; (c)<br />

unutrašnja struktura.<br />

Registar sa Sl. 2‐17 čine četiri razreda, gde svaki razred odgovara jednoj bit‐poziciji i sastoji se od<br />

jednog flip‐flopa i multipleksera 4‐u‐1. Postoje tri tipa razreda, koji se neznatno razlikuju u strukturi:<br />

krajnji levi, krajnji desni i srednji. Srednji razredi se obično projektuju prvi, pošto je njihova funkcija<br />

najočiglednija. Na primer, jednačine ulaza flip‐flopova za svaki od tri tipa razreda, dobijene na osnovu<br />

tabele operacija sa Sl. 2‐17(c) imaju sledeći oblik:<br />

̅ ̅ ̅ ̅ ̅ ̅ ̅ ̅ ,12 ̅ ̅ ̅ ̅ 47<br />

(c)<br />

I3 I2 I1 I0<br />

3 2 1 0<br />

mux<br />

3 2 1 0<br />

mux<br />

3 2 1 0<br />

mux<br />

D3 Q3 D2 Q2 D1 Q1 D0 Q0<br />

Q3 Q2 Q1 Q0<br />

IR