Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

se prelazi dešavaju u trenutku delovanja ivice taktnog signala, svako stanje se može tretirati kao<br />

vremenski interval između dve rastuće ivice taktnog signala.<br />

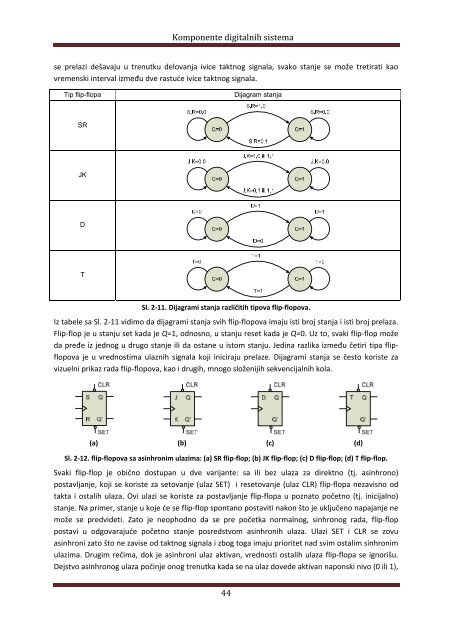

Tip flip-flopa Dijagram stanja<br />

SR<br />

JK<br />

D<br />

T<br />

Sl. 2‐11. Dijagrami stanja različitih tipova flip‐flopova.<br />

Iz tabele sa Sl. 2‐11 vidimo da dijagrami stanja svih flip‐flopova imaju isti broj stanja i isti broj prelaza.<br />

Flip‐flop je u stanju set kada je Q=1, odnosno, u stanju reset kada je Q=0. Uz to, svaki flip‐flop može<br />

da pređe iz jednog u drugo stanje ili da ostane u istom stanju. Jedina razlika između četiri tipa flip‐<br />

flopova je u vrednostima ulaznih signala koji iniciraju prelaze. Dijagrami stanja se često koriste za<br />

vizuelni prikaz rada flip‐flopova, kao i drugih, mnogo složenijih sekvencijalnih kola.<br />

(a) (b) (c) (d)<br />

Sl. 2‐12. flip‐flopova sa asinhronim ulazima: (a) SR flip‐flop; (b) JK flip‐flop; (c) D flip‐flop; (d) T flip‐flop.<br />

Svaki flip‐flop je obično dostupan u dve varijante: sa ili bez ulaza za direktno (tj. asinhrono)<br />

postavljanje, koji se koriste za setovanje (ulaz SET) i resetovanje (ulaz CLR) flip‐flopa nezavisno od<br />

takta i ostalih ulaza. Ovi ulazi se koriste za postavljanje flip‐flopa u poznato početno (tj. inicijalno)<br />

stanje. Na primer, stanje u koje će se flip‐flop spontano postaviti nakon što je uključeno napajanje ne<br />

može se predvideti. Zato je neophodno da se pre početka normalnog, sinhronog rada, flip‐flop<br />

postavi u odgovarajuće početno stanje posredstvom asinhronih ulaza. Ulazi SET i CLR se zovu<br />

asinhroni zato što ne zavise od taktnog signala i zbog toga imaju prioritet nad svim ostalim sinhronim<br />

ulazima. Drugim rečima, dok je asinhroni ulaz aktivan, vrednosti ostalih ulaza flip‐flopa se ignorišu.<br />

Dejstvo asinhronog ulaza počinje onog trenutka kada se na ulaz dovede aktivan naponski nivo (0 ili 1),<br />

44