Komponente digitalnih sistema

Komponente digitalnih sistema

Komponente digitalnih sistema

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Komponente</strong> <strong>digitalnih</strong> <strong>sistema</strong><br />

Svrha izlazne logike je generisanje signala Full i Empty. Red čekanja je prazan (Empty=1) ako je stanje<br />

brojača 111, a pun (Full=1) ako je stanje brojača 011. U svim ostalim stanjima brojača, oba signala,<br />

Full i Empty, imaju vrednost 0. Dakle:<br />

<br />

<br />

2.2.8.2 Realizacija na bazi RAM-a<br />

Kao i kod steka, redovi čekanja veće dužine, obično, umesto pomeračkih registara, za smeštanje<br />

podataka koriste RAM i sadrže dva brojača koji ukazuju na početak i kraj reda. Takva jedna struktura<br />

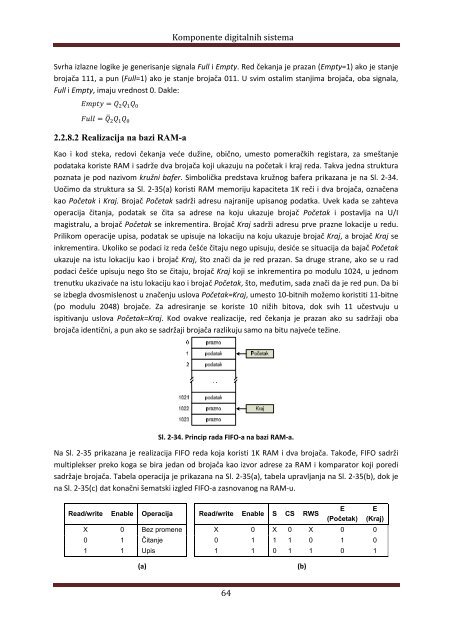

poznata je pod nazivom kružni bafer. Simbolička predstava kružnog bafera prikazana je na Sl. 2‐34.<br />

Uočimo da struktura sa Sl. 2‐35(a) koristi RAM memoriju kapaciteta 1K reči i dva brojača, označena<br />

kao Početak i Kraj. Brojač Početak sadrži adresu najranije upisanog podatka. Uvek kada se zahteva<br />

operacija čitanja, podatak se čita sa adrese na koju ukazuje brojač Početak i postavlja na U/I<br />

magistralu, a brojač Početak se inkrementira. Brojač Kraj sadrži adresu prve prazne lokacije u redu.<br />

Prilikom operacije upisa, podatak se upisuje na lokaciju na koju ukazuje brojač Kraj, a brojač Kraj se<br />

inkrementira. Ukoliko se podaci iz reda češće čitaju nego upisuju, desiće se situacija da bajač Početak<br />

ukazuje na istu lokaciju kao i brojač Kraj, što znači da je red prazan. Sa druge strane, ako se u rad<br />

podaci češće upisuju nego što se čitaju, brojač Kraj koji se inkrementira po modulu 1024, u jednom<br />

trenutku ukazivaće na istu lokaciju kao i brojač Početak, što, međutim, sada znači da je red pun. Da bi<br />

se izbegla dvosmislenost u značenju uslova Početak=Kraj, umesto 10‐bitnih možemo koristiti 11‐bitne<br />

(po modulu 2048) brojače. Za adresiranje se koriste 10 nižih bitova, dok svih 11 učestvuju u<br />

ispitivanju uslova Početak=Kraj. Kod ovakve realizacije, red čekanja je prazan ako su sadržaji oba<br />

brojača identični, a pun ako se sadržaji brojača razlikuju samo na bitu najveće težine.<br />

Sl. 2‐34. Princip rada FIFO‐a na bazi RAM‐a.<br />

Na Sl. 2‐35 prikazana je realizacija FIFO reda koja koristi 1K RAM i dva brojača. Takođe, FIFO sadrži<br />

multiplekser preko koga se bira jedan od brojača kao izvor adrese za RAM i komparator koji poredi<br />

sadržaje brojača. Tabela operacija je prikazana na Sl. 2‐35(a), tabela upravljanja na Sl. 2‐35(b), dok je<br />

na Sl. 2‐35(c) dat konačni šematski izgled FIFO‐a zasnovanog na RAM‐u.<br />

Read/write Enable Operacija<br />

Read/write Enable S CS RWS<br />

64<br />

E<br />

(Početak)<br />

X 0 Bez promene X 0 X 0 X 0 0<br />

0 1 Čitanje 0 1 1 1 0 1 0<br />

1 1 Upis 1 1 0 1 1 0 1<br />

(a) (b)<br />

E<br />

(Kraj)