1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 4 Entwurf digitaler Schaltungen<br />

Verzögerungszeiten von Leitungen und Zellen sowie Kapazitäten. Darin ist auch die<br />

Verzögerung für den Takt, so dass bei Post-Layout-Simulationen (mit PrimeTime und<br />

Formality) die manuelle Eingabe nicht mehr erforderlich ist.<br />

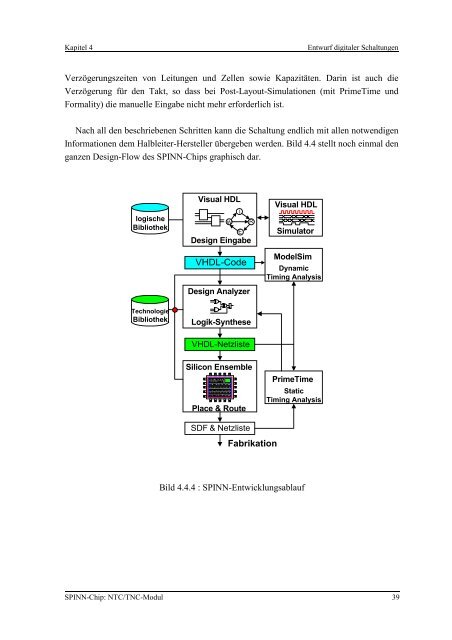

Nach all den beschriebenen Schritten kann die Schaltung endlich mit allen notwendigen<br />

Informationen dem Halbleiter-Hersteller übergeben werden. Bild 4.4 stellt noch einmal den<br />

ganzen Design-Flow des SPINN-Chips graphisch dar.<br />

logische<br />

Bibliothek<br />

Technologie<br />

Bibliothek<br />

Visual HDL<br />

W<br />

SPINN-Chip: NTC/TNC-Modul 39<br />

I<br />

E<br />

Design Eingabe<br />

VHDL-Code<br />

Design Analyzer<br />

Logik-Synthese<br />

VHDL-Netzliste<br />

Silicon Ensemble<br />

Place & Route<br />

SDF & Netzliste<br />

R<br />

Fabrikation<br />

Visual HDL<br />

Simulator<br />

ModelSim<br />

Dynamic<br />

Timing Analysis<br />

PrimeTime<br />

Static<br />

Timing Analysis<br />

Bild 4.4.4 : SPINN-Entwicklungsablauf