1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Kapitel 10 Zusammenfassung<br />

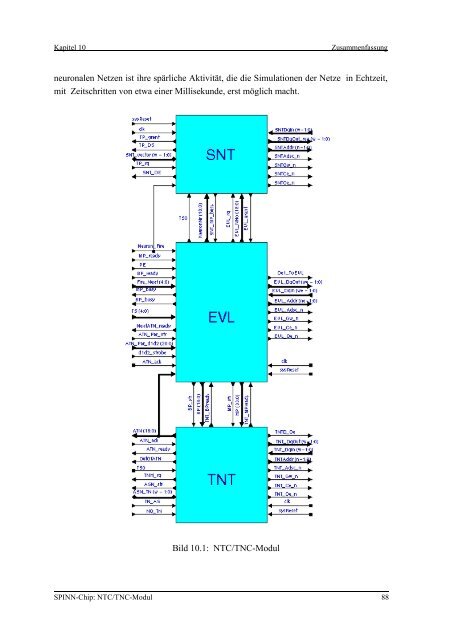

neuronalen Netzen ist ihre spärliche Aktivität, die die Simulationen der Netze in Echtzeit,<br />

mit Zeitschritten von etwa einer Millisekunde, erst möglich macht.<br />

Bild 10.1: NTC/TNC-Modul<br />

SPINN-Chip: NTC/TNC-Modul 88