1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

1. Einleitung - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

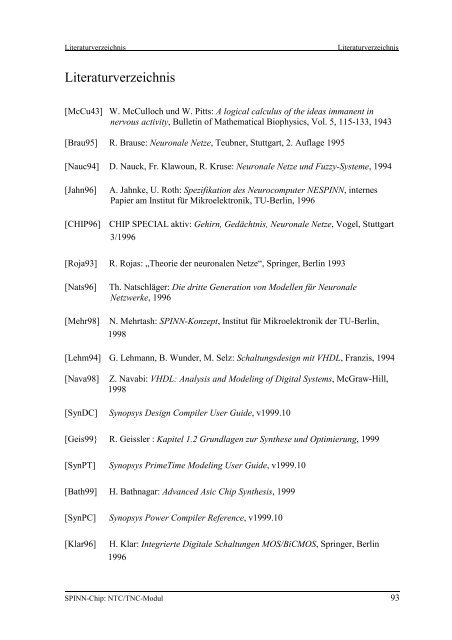

Literaturverzeichnis Literaturverzeichnis<br />

Literaturverzeichnis<br />

[McCu43] W. McCulloch und W. Pitts: A logical calculus of the ideas immanent in<br />

nervous activity, Bulletin of Mathematical Biophysics, Vol. 5, 115-133, 1943<br />

[Brau95] R. Brause: Neuronale Netze, Teubner, Stuttgart, 2. Auflage 1995<br />

[Nauc94] D. Nauck, Fr. Klawoun, R. Kruse: Neuronale Netze und Fuzzy-Systeme, 1994<br />

[Jahn96] A. Jahnke, U. Roth: Spezifikation des Neurocomputer NESPINN, internes<br />

Papier am Institut für <strong>Mikroelektronik</strong>, <strong>TU</strong>-<strong>Berlin</strong>, 1996<br />

[CHIP96] CHIP SPECIAL aktiv: Gehirn, Gedächtnis, Neuronale Netze, Vogel, Stuttgart<br />

3/1996<br />

[Roja93] R. Rojas: „Theorie der neuronalen Netze“, Springer, <strong>Berlin</strong> 1993<br />

[Nats96] Th. Natschläger: Die dritte Generation von Modellen für Neuronale<br />

Netzwerke, 1996<br />

[Mehr98] N. Mehrtash: SPINN-Konzept, Institut für <strong>Mikroelektronik</strong> der <strong>TU</strong>-<strong>Berlin</strong>,<br />

1998<br />

[Lehm94] G. Lehmann, B. Wunder, M. Selz: Schaltungsdesign mit VHDL, Franzis, 1994<br />

[Nava98] Z. Navabi: VHDL: Analysis and Modeling of Digital Systems, McGraw-Hill,<br />

1998<br />

[SynDC] Synopsys Design Compiler User Guide, v1999.10<br />

[Geis99} R. Geissler : Kapitel <strong>1.</strong>2 Grundlagen zur Synthese und Optimierung, 1999<br />

[SynPT] Synopsys PrimeTime Modeling User Guide, v1999.10<br />

[Bath99] H. Bathnagar: Advanced Asic Chip Synthesis, 1999<br />

[SynPC] Synopsys Power Compiler Reference, v1999.10<br />

[Klar96] H. Klar: Integrierte Digitale Schaltungen MOS/BiCMOS, Springer, <strong>Berlin</strong><br />

1996<br />

SPINN-Chip: NTC/TNC-Modul 93