{V}erifikation der diskreten - Embedded Systems Group

{V}erifikation der diskreten - Embedded Systems Group

{V}erifikation der diskreten - Embedded Systems Group

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

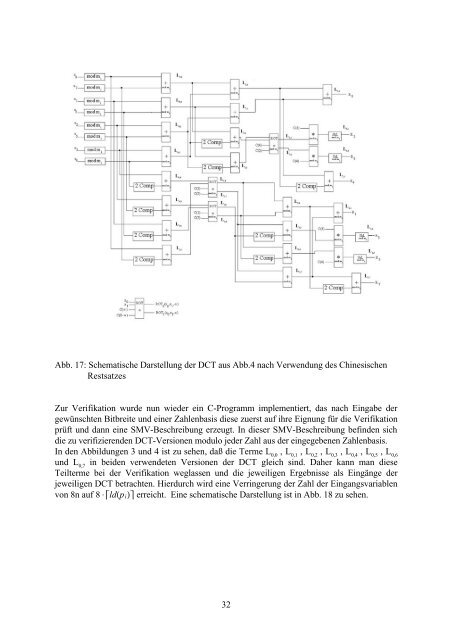

Abb. 17: Schematische Darstellung <strong>der</strong> DCT aus Abb.4 nach Verwendung des ChinesischenRestsatzesZur V<strong>erifikation</strong> wurde nun wie<strong>der</strong> ein C-Programm implementiert, das nach Eingabe <strong>der</strong>gewünschten Bitbreite und einer Zahlenbasis diese zuerst auf ihre Eignung für die V<strong>erifikation</strong>prüft und dann eine SMV-Beschreibung erzeugt. In dieser SMV-Beschreibung befinden sichdie zu verifizierenden DCT-Versionen modulo je<strong>der</strong> Zahl aus <strong>der</strong> eingegebenen Zahlenbasis.In den Abbildungen 3 und 4 ist zu sehen, daß die Terme L 0,0, L 0,1, L 0,2, L 0,3, L 0,4, L 0,5, L 0,6und L 0,7in beiden verwendeten Versionen <strong>der</strong> DCT gleich sind. Daher kann man dieseTeilterme bei <strong>der</strong> V<strong>erifikation</strong> weglassen und die jeweiligen Ergebnisse als Eingänge <strong>der</strong>jeweiligen DCT betrachten. Hierdurch wird eine Verringerung <strong>der</strong> Zahl <strong>der</strong> Eingangsvariablenvon 8n auf 8 ⋅ ⎡ld(p i )⎤ erreicht. Eine schematische Darstellung ist in Abb. 18 zu sehen.32