ARM710T processor

ARM710T processor

ARM710T processor

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

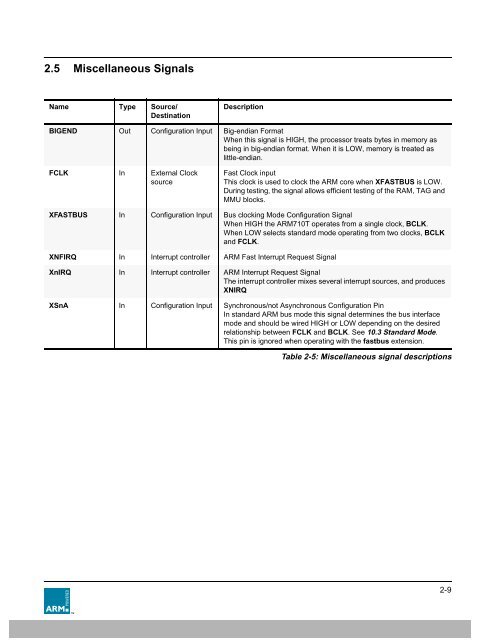

2.5 Miscellaneous Signals<br />

Name Type Source/<br />

Destination<br />

Description<br />

BIGEND Out Configuration Input Big-endian Format<br />

When this signal is HIGH, the <strong>processor</strong> treats bytes in memory as<br />

being in big-endian format. When it is LOW, memory is treated as<br />

little-endian.<br />

FCLK In External Clock<br />

source<br />

Fast Clock input<br />

This clock is used to clock the ARM core when XFASTBUS is LOW.<br />

During testing, the signal allows efficient testing of the RAM, TAG and<br />

MMU blocks.<br />

XFASTBUS In Configuration Input Bus clocking Mode Configuration Signal<br />

When HIGH the <strong>ARM710T</strong> operates from a single clock, BCLK.<br />

When LOW selects standard mode operating from two clocks, BCLK<br />

and FCLK.<br />

XNFIRQ In Interrupt controller ARM Fast Interrupt Request Signal<br />

XnIRQ In Interrupt controller ARM Interrupt Request Signal<br />

The interrupt controller mixes several interrupt sources, and produces<br />

XNIRQ<br />

XSnA In Configuration Input Synchronous/not Asynchronous Configuration Pin<br />

In standard ARM bus mode this signal determines the bus interface<br />

mode and should be wired HIGH or LOW depending on the desired<br />

relationship between FCLK and BCLK. See 10.3 Standard Mode.<br />

This pin is ignored when operating with the fastbus extension.<br />

Table 2-5: Miscellaneous signal descriptions<br />

2-9