digital compensation of dynamic acquisition errors at the front-end of ...

digital compensation of dynamic acquisition errors at the front-end of ...

digital compensation of dynamic acquisition errors at the front-end of ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

2 Chapter 1: Introduction<br />

BPF<br />

LO1<br />

BPF<br />

LPF<br />

LO2<br />

+90 ◦ LPF<br />

ADC<br />

ADC<br />

I<br />

Q<br />

Analog<br />

Digital<br />

LPF<br />

I<br />

BPF<br />

LO1<br />

BPF<br />

ADC<br />

+90 ◦<br />

LO2<br />

LPF<br />

Q<br />

Analog<br />

Digital<br />

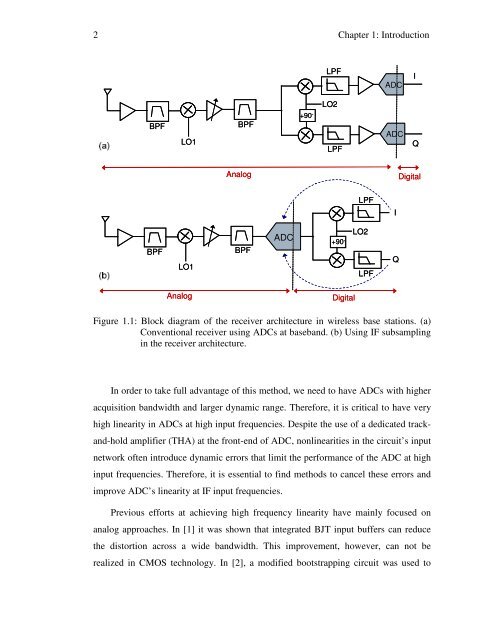

Figure 1.1: Block diagram <strong>of</strong> <strong>the</strong> receiver architecture in wireless base st<strong>at</strong>ions. (a)<br />

Conventional receiver using ADCs <strong>at</strong> baseband. (b) Using IF subsampling<br />

in <strong>the</strong> receiver architecture.<br />

In order to take full advantage <strong>of</strong> this method, we need to have ADCs with higher<br />

<strong>acquisition</strong> bandwidth and larger <strong>dynamic</strong> range. Therefore, it is critical to have very<br />

high linearity in ADCs <strong>at</strong> high input frequencies. Despite <strong>the</strong> use <strong>of</strong> a dedic<strong>at</strong>ed trackand-hold<br />

amplifier (THA) <strong>at</strong> <strong>the</strong> <strong>front</strong>-<strong>end</strong> <strong>of</strong> ADC, nonlinearities in <strong>the</strong> circuit’s input<br />

network <strong>of</strong>ten introduce <strong>dynamic</strong> <strong>errors</strong> th<strong>at</strong> limit <strong>the</strong> performance <strong>of</strong> <strong>the</strong> ADC <strong>at</strong> high<br />

input frequencies. Therefore, it is essential to find methods to cancel <strong>the</strong>se <strong>errors</strong> and<br />

improve ADC’s linearity <strong>at</strong> IF input frequencies.<br />

Previous efforts <strong>at</strong> achieving high frequency linearity have mainly focused on<br />

analog approaches. In [1] it was shown th<strong>at</strong> integr<strong>at</strong>ed BJT input buffers can reduce<br />

<strong>the</strong> distortion across a wide bandwidth. This improvement, however, can not be<br />

realized in CMOS technology. In [2], a modified bootstrapping circuit was used to