digital compensation of dynamic acquisition errors at the front-end of ...

digital compensation of dynamic acquisition errors at the front-end of ...

digital compensation of dynamic acquisition errors at the front-end of ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

4 Chapter 1: Introduction<br />

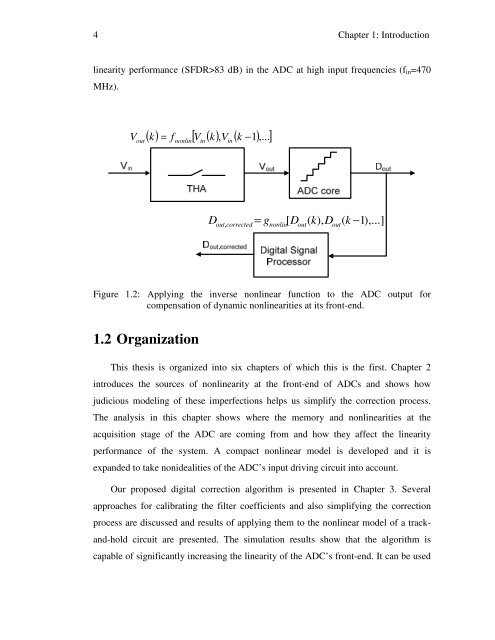

linearity performance (SFDR>83 dB) in <strong>the</strong> ADC <strong>at</strong> high input frequencies (f in =470<br />

MHz).<br />

V<br />

out<br />

( k) = f [ V ( k) , V ( k −1 ),...]<br />

nonlin<br />

in<br />

in<br />

D<br />

out<br />

, corrected<br />

= gnonlin[<br />

Dout<br />

( k),<br />

Dout<br />

( k −1),...]<br />

Figure 1.2: Applying <strong>the</strong> inverse nonlinear function to <strong>the</strong> ADC output for<br />

<strong>compens<strong>at</strong>ion</strong> <strong>of</strong> <strong>dynamic</strong> nonlinearities <strong>at</strong> its <strong>front</strong>-<strong>end</strong>.<br />

1.2 Organiz<strong>at</strong>ion<br />

This <strong>the</strong>sis is organized into six chapters <strong>of</strong> which this is <strong>the</strong> first. Chapter 2<br />

introduces <strong>the</strong> sources <strong>of</strong> nonlinearity <strong>at</strong> <strong>the</strong> <strong>front</strong>-<strong>end</strong> <strong>of</strong> ADCs and shows how<br />

judicious modeling <strong>of</strong> <strong>the</strong>se imperfections helps us simplify <strong>the</strong> correction process.<br />

The analysis in this chapter shows where <strong>the</strong> memory and nonlinearities <strong>at</strong> <strong>the</strong><br />

<strong>acquisition</strong> stage <strong>of</strong> <strong>the</strong> ADC are coming from and how <strong>the</strong>y affect <strong>the</strong> linearity<br />

performance <strong>of</strong> <strong>the</strong> system. A compact nonlinear model is developed and it is<br />

expanded to take nonidealities <strong>of</strong> <strong>the</strong> ADC’s input driving circuit into account.<br />

Our proposed <strong>digital</strong> correction algorithm is presented in Chapter 3. Several<br />

approaches for calibr<strong>at</strong>ing <strong>the</strong> filter coefficients and also simplifying <strong>the</strong> correction<br />

process are discussed and results <strong>of</strong> applying <strong>the</strong>m to <strong>the</strong> nonlinear model <strong>of</strong> a trackand-hold<br />

circuit are presented. The simul<strong>at</strong>ion results show th<strong>at</strong> <strong>the</strong> algorithm is<br />

capable <strong>of</strong> significantly increasing <strong>the</strong> linearity <strong>of</strong> <strong>the</strong> ADC’s <strong>front</strong>-<strong>end</strong>. It can be used