ARM Processor Instruction Set

ARM Processor Instruction Set

ARM Processor Instruction Set

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>ARM</strong> <strong>Processor</strong> <strong>Instruction</strong> <strong>Set</strong><br />

31<br />

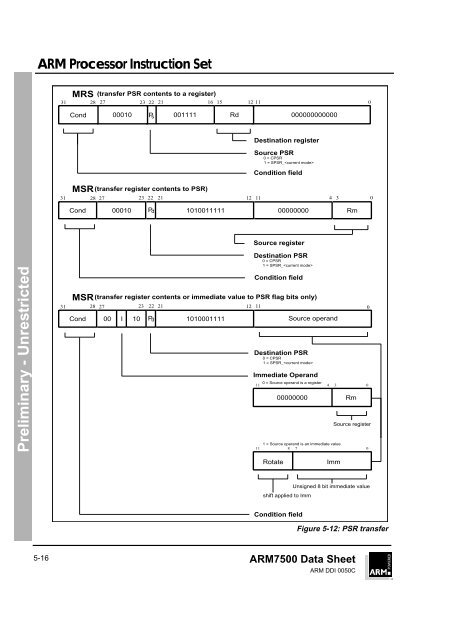

MRS<br />

(transfer PSR contents to a register)<br />

28 27<br />

23 22 21<br />

16 15<br />

12 11<br />

0<br />

Cond<br />

00010 Ps 001111 Rd<br />

000000000000<br />

Destination register<br />

Source PSR<br />

0 = CPSR<br />

1 = SPSR_<br />

Condition field<br />

Preliminary - Unrestricted<br />

MSR<br />

(transfer register contents to PSR)<br />

4 3<br />

31 28 27<br />

23 22 21<br />

12 11<br />

Cond 00010 P d 1010011111 00000000<br />

Cond 00 I 10 P d 1010001111<br />

Source operand<br />

Source register<br />

Destination PSR<br />

0 = CPSR<br />

1 = SPSR_<br />

Condition field<br />

MSR (transfer register contents or immediate value to PSR flag bits only)<br />

31 28 27<br />

23 22 21 12 11<br />

Destination PSR<br />

0 = CPSR<br />

1 = SPSR_<br />

Immediate Operand<br />

0 = Source operand is a register<br />

11<br />

00000000<br />

Rm<br />

Rm<br />

1 = Source operand is an immediate value<br />

11 8 7 0<br />

4<br />

3<br />

0<br />

0<br />

Source register<br />

0<br />

Rotate<br />

Imm<br />

shift applied to Imm<br />

Unsigned 8 bit immediate value<br />

Condition field<br />

Figure 5-12: PSR transfer<br />

5-16<br />

<strong>ARM</strong>7500 Data Sheet<br />

<strong>ARM</strong> DDI 0050C