ARM Processor Instruction Set

ARM Processor Instruction Set

ARM Processor Instruction Set

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>ARM</strong> <strong>Processor</strong> <strong>Instruction</strong> <strong>Set</strong><br />

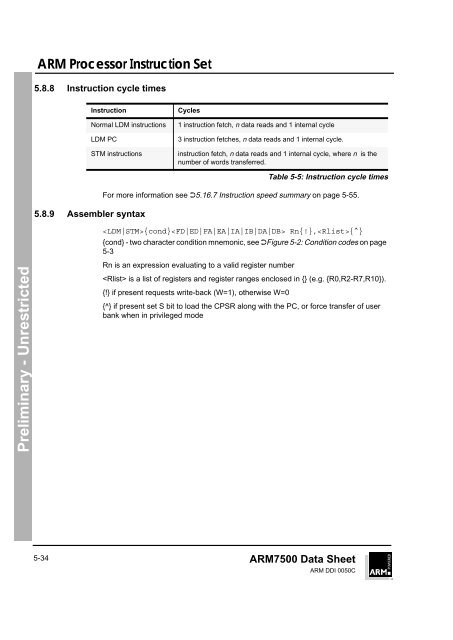

5.8.8 <strong>Instruction</strong> cycle times<br />

<strong>Instruction</strong><br />

Normal LDM instructions<br />

LDM PC<br />

STM instructions<br />

Cycles<br />

1 instruction fetch, n data reads and 1 internal cycle<br />

3 instruction fetches, n data reads and 1 internal cycle.<br />

instruction fetch, n data reads and 1 internal cycle, where n is the<br />

number of words transferred.<br />

5.8.9 Assembler syntax<br />

Table 5-5: <strong>Instruction</strong> cycle times<br />

For more information see ➲5.16.7 <strong>Instruction</strong> speed summary on page 5-55.<br />

{cond} Rn{!},{^}<br />

{cond} - two character condition mnemonic, see ➲Figure 5-2: Condition codes on page<br />

5-3<br />

Preliminary - Unrestricted<br />

Rn is an expression evaluating to a valid register number<br />

is a list of registers and register ranges enclosed in {} (e.g. {R0,R2-R7,R10}).<br />

{!} if present requests write-back (W=1), otherwise W=0<br />

{^} if present set S bit to load the CPSR along with the PC, or force transfer of user<br />

bank when in privileged mode<br />

5-34<br />

<strong>ARM</strong>7500 Data Sheet<br />

<strong>ARM</strong> DDI 0050C