ARM Processor Instruction Set

ARM Processor Instruction Set

ARM Processor Instruction Set

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>ARM</strong> <strong>Processor</strong> <strong>Instruction</strong> <strong>Set</strong><br />

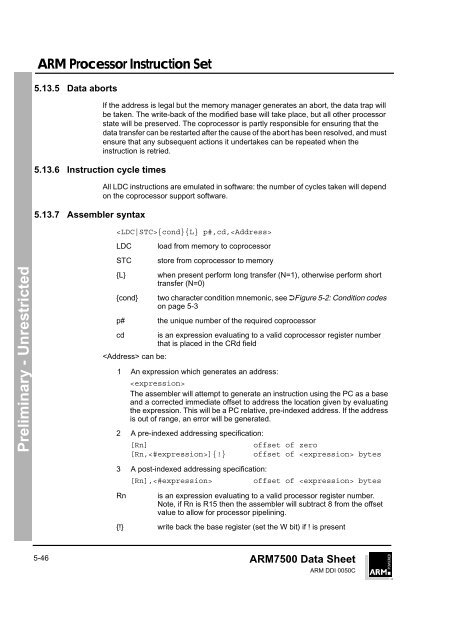

5.13.5 Data aborts<br />

5.13.6 <strong>Instruction</strong> cycle times<br />

5.13.7 Assembler syntax<br />

If the address is legal but the memory manager generates an abort, the data trap will<br />

be taken. The write-back of the modified base will take place, but all other processor<br />

state will be preserved. The coprocessor is partly responsible for ensuring that the<br />

data transfer can be restarted after the cause of the abort has been resolved, and must<br />

ensure that any subsequent actions it undertakes can be repeated when the<br />

instruction is retried.<br />

All LDC instructions are emulated in software: the number of cycles taken will depend<br />

on the coprocessor support software.<br />

{cond}{L} p#,cd,<br />

Preliminary - Unrestricted<br />

LDC<br />

STC<br />

{L}<br />

{cond}<br />

load from memory to coprocessor<br />

store from coprocessor to memory<br />

when present perform long transfer (N=1), otherwise perform short<br />

transfer (N=0)<br />

two character condition mnemonic, see ➲Figure 5-2: Condition codes<br />

on page 5-3<br />

p# the unique number of the required coprocessor<br />

cd<br />

can be:<br />

is an expression evaluating to a valid coprocessor register number<br />

that is placed in the CRd field<br />

1 An expression which generates an address:<br />

<br />

The assembler will attempt to generate an instruction using the PC as a base<br />

and a corrected immediate offset to address the location given by evaluating<br />

the expression. This will be a PC relative, pre-indexed address. If the address<br />

is out of range, an error will be generated.<br />

2 A pre-indexed addressing specification:<br />

[Rn]<br />

[Rn,]{!}<br />

offset of zero<br />

offset of bytes<br />

3 A post-indexed addressing specification:<br />

Rn<br />

[Rn],<br />

offset of bytes<br />

is an expression evaluating to a valid processor register number.<br />

Note, if Rn is R15 then the assembler will subtract 8 from the offset<br />

value to allow for processor pipelining.<br />

{!} write back the base register (set the W bit) if ! is present<br />

5-46<br />

<strong>ARM</strong>7500 Data Sheet<br />

<strong>ARM</strong> DDI 0050C