ARM Processor Instruction Set

ARM Processor Instruction Set

ARM Processor Instruction Set

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>ARM</strong> <strong>Processor</strong> <strong>Instruction</strong> <strong>Set</strong><br />

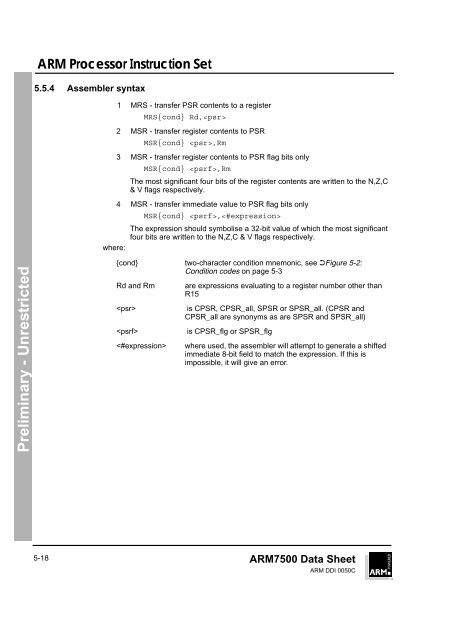

5.5.4 Assembler syntax<br />

where:<br />

1 MRS - transfer PSR contents to a register<br />

MRS{cond} Rd,<br />

2 MSR - transfer register contents to PSR<br />

MSR{cond} ,Rm<br />

3 MSR - transfer register contents to PSR flag bits only<br />

MSR{cond} ,Rm<br />

The most significant four bits of the register contents are written to the N,Z,C<br />

& V flags respectively.<br />

4 MSR - transfer immediate value to PSR flag bits only<br />

MSR{cond} ,<br />

The expression should symbolise a 32-bit value of which the most significant<br />

four bits are written to the N,Z,C & V flags respectively.<br />

Preliminary - Unrestricted<br />

{cond} two-character condition mnemonic, see ➲Figure 5-2:<br />

Condition codes on page 5-3<br />

Rd and Rm<br />

are expressions evaluating to a register number other than<br />

R15<br />

is CPSR, CPSR_all, SPSR or SPSR_all. (CPSR and<br />

CPSR_all are synonyms as are SPSR and SPSR_all)<br />

is CPSR_flg or SPSR_flg<br />

<br />

where used, the assembler will attempt to generate a shifted<br />

immediate 8-bit field to match the expression. If this is<br />

impossible, it will give an error.<br />

5-18<br />

<strong>ARM</strong>7500 Data Sheet<br />

<strong>ARM</strong> DDI 0050C