ARM Processor Instruction Set

ARM Processor Instruction Set

ARM Processor Instruction Set

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>ARM</strong> <strong>Processor</strong> <strong>Instruction</strong> <strong>Set</strong><br />

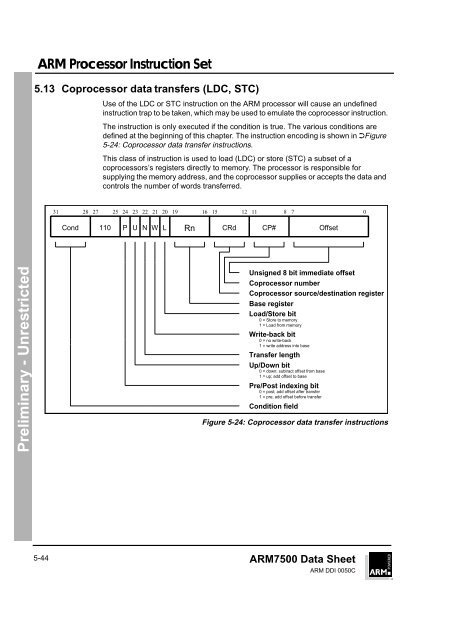

5.13 Coprocessor data transfers (LDC, STC)<br />

Use of the LDC or STC instruction on the <strong>ARM</strong> processor will cause an undefined<br />

instruction trap to be taken, which may be used to emulate the coprocessor instruction.<br />

The instruction is only executed if the condition is true. The various conditions are<br />

defined at the beginning of this chapter. The instruction encoding is shown in ➲Figure<br />

5-24: Coprocessor data transfer instructions.<br />

This class of instruction is used to load (LDC) or store (STC) a subset of a<br />

coprocessors’s registers directly to memory. The processor is responsible for<br />

supplying the memory address, and the coprocessor supplies or accepts the data and<br />

controls the number of words transferred.<br />

31<br />

28<br />

27<br />

25<br />

24<br />

23<br />

22<br />

21<br />

20<br />

19<br />

16<br />

15<br />

12<br />

11<br />

8<br />

7<br />

0<br />

Cond<br />

110 P U N W L Rn CRd CP# Offset<br />

Preliminary - Unrestricted<br />

Unsigned 8 bit immediate offset<br />

Coprocessor number<br />

Coprocessor source/destination register<br />

Base register<br />

Load/Store bit<br />

0 = Store to memory<br />

1 = Load from memory<br />

Write-back bit<br />

0 = no write-back<br />

1 = write address into base<br />

Transfer length<br />

Up/Down bit<br />

0 = down; subtract offset from base<br />

1 = up; add offset to base<br />

Pre/Post indexing bit<br />

0 = post; add offset after transfer<br />

1 = pre; add offset before transfer<br />

Condition field<br />

Figure 5-24: Coprocessor data transfer instructions<br />

5-44<br />

<strong>ARM</strong>7500 Data Sheet<br />

<strong>ARM</strong> DDI 0050C