Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Digital</strong> <strong>Subscriber</strong> <strong>Line</strong> <strong>Access</strong> <strong>Multiplexer</strong> (<strong>DSLAM</strong>) <strong>Example</strong> <strong>Design</strong><br />

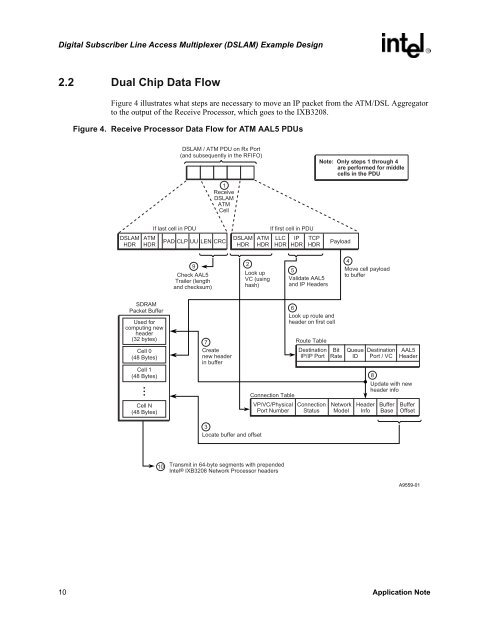

2.2 Dual Chip Data Flow<br />

Figure 4 illustrates what steps are necessary to move an IP packet from the ATM/DSL Aggregator<br />

to the output of the Receive Processor, which goes to the IXB3208.<br />

Figure 4. Receive Processor Data Flow for ATM AAL5 PDUs<br />

<strong>DSLAM</strong> / ATM PDU on Rx Port<br />

(and subsequently in the RFIFO)<br />

Note: Only steps 1 through 4<br />

are performed for middle<br />

cells in the PDU<br />

1<br />

Receive<br />

<strong>DSLAM</strong><br />

ATM<br />

Cell<br />

<strong>DSLAM</strong><br />

HDR<br />

ATM<br />

HDR<br />

If last cell in PDU<br />

PAD CLP<br />

UU LEN CRC<br />

<strong>DSLAM</strong><br />

HDR<br />

ATM<br />

HDR<br />

If first cell in PDU<br />

LLC<br />

HDR<br />

IP<br />

HDR<br />

TCP<br />

HDR<br />

Payload<br />

9<br />

Check AAL5<br />

Trailer (length<br />

and checksum)<br />

2<br />

Look up<br />

VC (using<br />

hash)<br />

5<br />

Validate AAL5<br />

and IP Headers<br />

4<br />

Move cell payload<br />

to buffer<br />

SDRAM<br />

Packet Buffer<br />

Used for<br />

computing new<br />

header<br />

(32 bytes)<br />

Cell 0<br />

(48 Bytes)<br />

Cell 1<br />

(48 Bytes)<br />

Cell N<br />

(48 Bytes)<br />

7<br />

Create<br />

new header<br />

in buffer<br />

Connection Table<br />

VP/VC/Physical<br />

Port Number<br />

6<br />

Look up route and<br />

header on first cell<br />

Route Table<br />

Destination<br />

IP/IP Port<br />

Connection<br />

Status<br />

Bit<br />

Rate<br />

Network<br />

Model<br />

Queue<br />

ID<br />

Header<br />

Info<br />

Destination<br />

Port / VC<br />

8<br />

Update with new<br />

header info<br />

Buffer<br />

Base<br />

AAL5<br />

Header<br />

Buffer<br />

Offset<br />

3<br />

Locate buffer and offset<br />

10<br />

Transmit in 64-byte segments with prepended<br />

Intel® IXB3208 Network Processor headers<br />

A9559-01<br />

10 Application Note