Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

Digital Subscriber Line Access Multiplexer (DSLAM) Example Design

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Digital</strong> <strong>Subscriber</strong> <strong>Line</strong> <strong>Access</strong> <strong>Multiplexer</strong> (<strong>DSLAM</strong>) <strong>Example</strong> <strong>Design</strong><br />

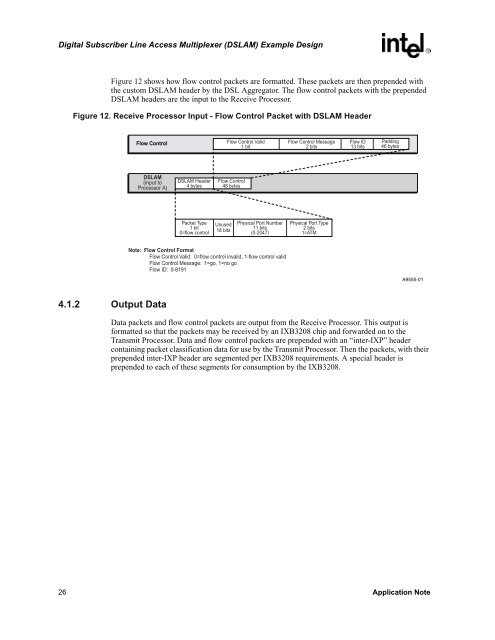

Figure 12 shows how flow control packets are formatted. These packets are then prepended with<br />

the custom <strong>DSLAM</strong> header by the DSL Aggregator. The flow control packets with the prepended<br />

<strong>DSLAM</strong> headers are the input to the Receive Processor.<br />

Figure 12. Receive Processor Input - Flow Control Packet with <strong>DSLAM</strong> Header<br />

Flow Control<br />

Flow Control Valid<br />

1 bit<br />

Flow Control Message<br />

2 bits<br />

Flow ID<br />

13 bits<br />

Padding<br />

46 bytes<br />

<strong>DSLAM</strong><br />

(input to<br />

Processor A)<br />

<strong>DSLAM</strong> Header<br />

4 bytes<br />

Flow Control<br />

48 bytes<br />

Packet Type<br />

1 bit<br />

0=flow control<br />

Unused<br />

18 bits<br />

Physical Port Number<br />

11 bits<br />

(0-2047)<br />

Physical Port Type<br />

2 bits<br />

1=ATM<br />

Note: Flow Control Format<br />

Flow Control Valid: 0=flow control invalid, 1-flow control valid<br />

Flow Control Message: 1=go, 1=no go<br />

Flow ID: 0-8191<br />

A9555-01<br />

4.1.2 Output Data<br />

Data packets and flow control packets are output from the Receive Processor. This output is<br />

formatted so that the packets may be received by an IXB3208 chip and forwarded on to the<br />

Transmit Processor. Data and flow control packets are prepended with an “inter-IXP” header<br />

containing packet classification data for use by the Transmit Processor. Then the packets, with their<br />

prepended inter-IXP header are segmented per IXB3208 requirements. A special header is<br />

prepended to each of these segments for consumption by the IXB3208.<br />

26 Application Note