Is Parallel Programming Hard, And, If So, What Can You Do About It?

Is Parallel Programming Hard, And, If So, What Can You Do About It?

Is Parallel Programming Hard, And, If So, What Can You Do About It?

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

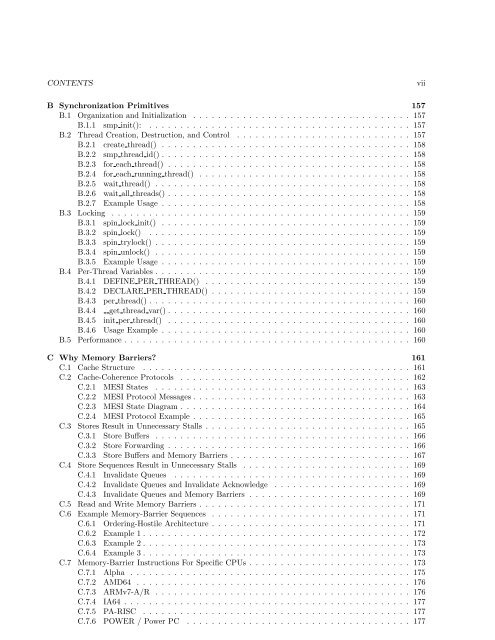

CONTENTSviiB Synchronization Primitives 157B.1 Organization and Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157B.1.1 smp init(): . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157B.2 Thread Creation, Destruction, and Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157B.2.1 create thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.2 smp thread id() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.3 for each thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.4 for each running thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.5 wait thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.6 wait all threads() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.2.7 Example Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158B.3 Locking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.3.1 spin lock init() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.3.2 spin lock() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.3.3 spin trylock() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.3.4 spin unlock() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.3.5 Example Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.4 Per-Thread Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.4.1 DEFINE PER THREAD() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.4.2 DECLARE PER THREAD() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159B.4.3 per thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160B.4.4 get thread var() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160B.4.5 init per thread() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160B.4.6 Usage Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160B.5 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160C Why Memory Barriers? 161C.1 Cache Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161C.2 Cache-Coherence Protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162C.2.1 MESI States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163C.2.2 MESI Protocol Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163C.2.3 MESI State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164C.2.4 MESI Protocol Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165C.3 Stores Result in Unnecessary Stalls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165C.3.1 Store Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166C.3.2 Store Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166C.3.3 Store Buffers and Memory Barriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167C.4 Store Sequences Result in Unnecessary Stalls . . . . . . . . . . . . . . . . . . . . . . . . . . . 169C.4.1 Invalidate Queues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169C.4.2 Invalidate Queues and Invalidate Acknowledge . . . . . . . . . . . . . . . . . . . . . . 169C.4.3 Invalidate Queues and Memory Barriers . . . . . . . . . . . . . . . . . . . . . . . . . . 169C.5 Read and Write Memory Barriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171C.6 Example Memory-Barrier Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171C.6.1 Ordering-Hostile Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171C.6.2 Example 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172C.6.3 Example 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173C.6.4 Example 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173C.7 Memory-Barrier Instructions For Specific CPUs . . . . . . . . . . . . . . . . . . . . . . . . . . 173C.7.1 Alpha . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175C.7.2 AMD64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176C.7.3 ARMv7-A/R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176C.7.4 IA64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177C.7.5 PA-RISC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177C.7.6 POWER / Power PC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

![Debugging with Ptkdb [pdf] - CPAN](https://img.yumpu.com/38177199/1/190x247/debugging-with-ptkdb-pdf-cpan.jpg?quality=85)