Nios II Processor Reference Handbook

Nios II Processor Reference Handbook

Nios II Processor Reference Handbook

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

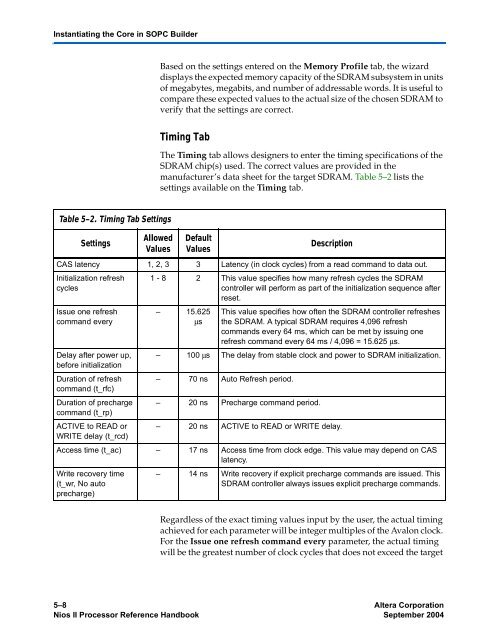

Instantiating the Core in SOPC BuilderBased on the settings entered on the Memory Profile tab, the wizarddisplays the expected memory capacity of the SDRAM subsystem in unitsof megabytes, megabits, and number of addressable words. It is useful tocompare these expected values to the actual size of the chosen SDRAM toverify that the settings are correct.Timing TabThe Timing tab allows designers to enter the timing specifications of theSDRAM chip(s) used. The correct values are provided in themanufacturer’s data sheet for the target SDRAM. Table 5–2 lists thesettings available on the Timing tab.Table 5–2. Timing Tab SettingsSettingsAllowedValuesDefaultValuesDescriptionCAS latency 1, 2, 3 3 Latency (in clock cycles) from a read command to data out.Initialization refreshcyclesIssue one refreshcommand everyDelay after power up,before initializationDuration of refreshcommand (t_rfc)Duration of prechargecommand (t_rp)ACTIVE to READ orWRITE delay (t_rcd)1 - 8 2 This value specifies how many refresh cycles the SDRAMcontroller will perform as part of the initialization sequence afterreset.– 15.625µsThis value specifies how often the SDRAM controller refreshesthe SDRAM. A typical SDRAM requires 4,096 refreshcommands every 64 ms, which can be met by issuing onerefresh command every 64 ms / 4,096 = 15.625 µs.– 100 µs The delay from stable clock and power to SDRAM initialization.– 70 ns Auto Refresh period.– 20 ns Precharge command period.– 20 ns ACTIVE to READ or WRITE delay.Access time (t_ac) – 17 ns Access time from clock edge. This value may depend on CASlatency.Write recovery time(t_wr, No autoprecharge)– 14 ns Write recovery if explicit precharge commands are issued. ThisSDRAM controller always issues explicit precharge commands.Regardless of the exact timing values input by the user, the actual timingachieved for each parameter will be integer multiples of the Avalon clock.For the Issue one refresh command every parameter, the actual timingwill be the greatest number of clock cycles that does not exceed the target5–8 Altera Corporation<strong>Nios</strong> <strong>II</strong> <strong>Processor</strong> <strong>Reference</strong> <strong>Handbook</strong> September 2004