Nios II Processor Reference Handbook

Nios II Processor Reference Handbook

Nios II Processor Reference Handbook

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

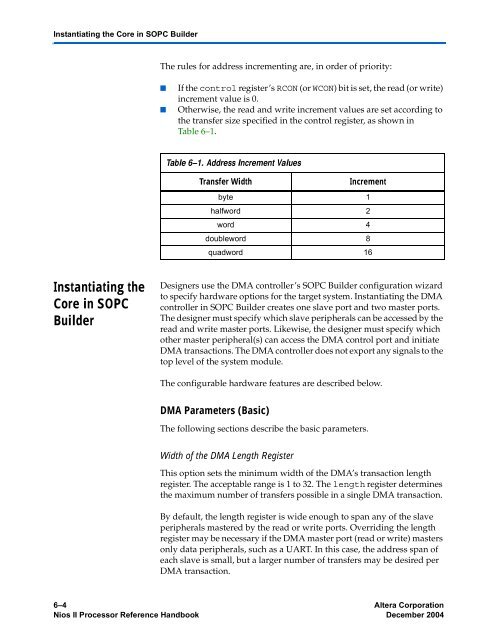

Instantiating the Core in SOPC BuilderThe rules for address incrementing are, in order of priority:■■If the control register’s RCON (or WCON) bit is set, the read (or write)increment value is 0.Otherwise, the read and write increment values are set according tothe transfer size specified in the control register, as shown inTable 6–1.Table 6–1. Address Increment ValuesTransfer WidthIncrementbyte 1halfword 2word 4doubleword 8quadword 16Instantiating theCore in SOPCBuilderDesigners use the DMA controller’s SOPC Builder configuration wizardto specify hardware options for the target system. Instantiating the DMAcontroller in SOPC Builder creates one slave port and two master ports.The designer must specify which slave peripherals can be accessed by theread and write master ports. Likewise, the designer must specify whichother master peripheral(s) can access the DMA control port and initiateDMA transactions. The DMA controller does not export any signals to thetop level of the system module.The configurable hardware features are described below.DMA Parameters (Basic)The following sections describe the basic parameters.Width of the DMA Length RegisterThis option sets the minimum width of the DMA’s transaction lengthregister. The acceptable range is 1 to 32. The length register determinesthe maximum number of transfers possible in a single DMA transaction.By default, the length register is wide enough to span any of the slaveperipherals mastered by the read or write ports. Overriding the lengthregister may be necessary if the DMA master port (read or write) mastersonly data peripherals, such as a UART. In this case, the address span ofeach slave is small, but a larger number of transfers may be desired perDMA transaction.6–4 Altera Corporation<strong>Nios</strong> <strong>II</strong> <strong>Processor</strong> <strong>Reference</strong> <strong>Handbook</strong> December 2004